CAP S

POSITIVE CLAMP IN CAP >40 F

(4950)- CALIBRATE R STAGE 1

IR ١ STAGE 2

(INTERNAL) > ||

> I STAGE 3

C \

$\frac{IR}{I^{\dagger}} = \frac{\lambda}{C\lambda}$  So  $C = \frac{+}{R}$

C is calibrated — no offsets

I & V do not matter!

Notes - 1. STAGE 2&3 can be repeated at any time (5)

2. SELECTING CAP CAUSES STAGE 2&3 - hence delay, 0/P turns on & off, etc.

3. IF R is wrong then C is also wrong.

SELF CAL OF CAP

SC1

REMOVE / THERMISTOR CONNECTOR REPLACE

HEAT THERMISTOR

SELECT

CAP

CAL. ANY HI OHMS RANGE >40K,

WITH O/P = TARGET.

FORCING CAP SELF CALS

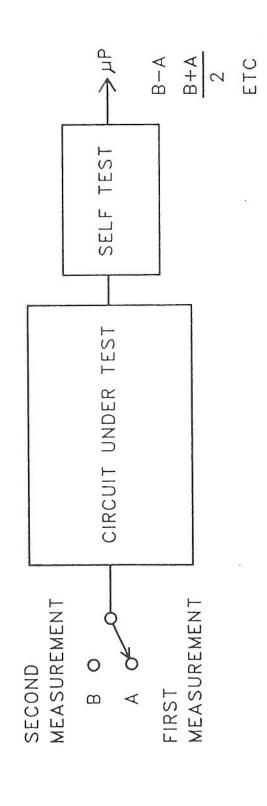

SELF TEST PRINCIPLE

SELF TEST A06.002

SELF TESTS A06.028 to A06.036

SELF TESTS A03.011 TO A03.018 +A06.041

ST5

ST6

# BEWARE ID DUE TO LIGHT!

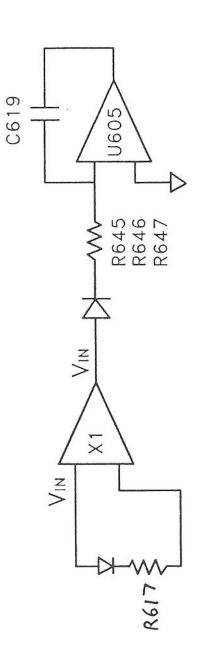

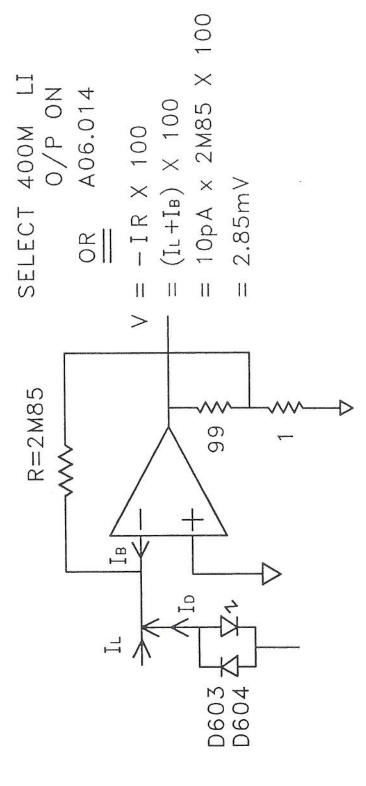

15 ---> VOLTS CONVERTER (BOARD, U605, U607,) RELAYS (≈A06.014) LOW CURRENT IBIAS TEST

INVERTING CHOPPER

## **OHMS & CAP Self Test Descriptions**

### A06,001

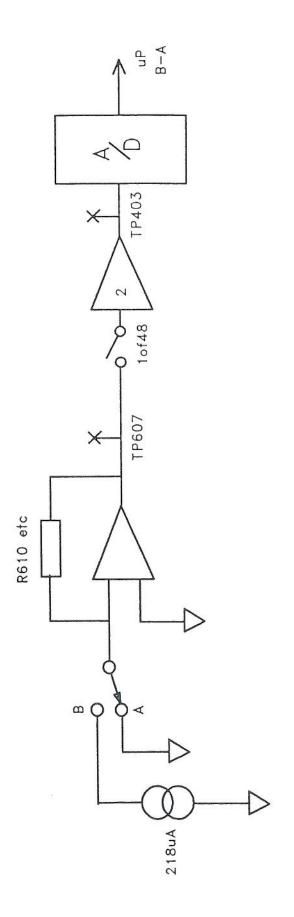

Check zero of composite amp U602 and U607.

Input = OFF Feedback = R610

If fails, check TP607 WRT TL401 (<50uV). Used for maths, establishing offset voltages.

### A06,002 to A06,013

These tests all apply zero (A) then INPUT (B).

The result is (B-A). Input is from U109 via 'TICKLE' (zero for A06.012 is in fact +1.1nA).

The table below gives the inputs and expected outputs on TP607 WRT TL401, with the resistor under test circuit designator.

| Test    | Input "Curtickle" | TP607   | Resistor         | Volts<br>to<br>/D (TP403) | Notes |

|---------|-------------------|---------|------------------|---------------------------|-------|

| A06.002 | +218uA            | -0.622V | R610             | +1.245V                   |       |

| A06.003 | -218uA            | +0.622V | R610             | - 1.245V                  |       |

| A06.004 | +21.8uA           | -0.622V | R609             | +1.245V                   |       |

| A06.005 | -21.8uA           | +0.622V | R609             | - 1.245V                  |       |

| A06.006 | +35.09uA          | -10V    | R608             | +2.00V                    | (1)   |

| A06.007 | -35.09uA          | +10V    | R608             | - 2.00V                   | (1)   |

| A06.008 | +2u18uA           | -6.22V  | R611 +R672       | +1.245V                   |       |

| A06.009 | -2u18uA           | +6.22V  | R611 +R672       | - 1.245V                  |       |

| A06.010 | +218nA            | -6.22V  | R611+R672+R668/5 | +1.245V                   | (2)   |

| A06.011 | -218nA            | +6.22V  | R611+R672+R668/5 | -1.245V                   | (2)   |

| A06.012 | +35.2nA           | -10V    | R611+R672+R668/1 | +2.00V                    | (3)   |

| A06.013 | -34.1nA           | +9.7V   | R611+R672+R668/1 | -1.94V                    | (3)   |

| A06.014 | 0nA               | 0V      | R611+R672+R668/1 | 0V                        | (4)   |

### Notes

- (1) Checks amp swings +/- also.

- (2) Note use of divider R668 Pin 5.

- (3) Checks clamp D607, D608 leakages are low.

- (4) Bias current test in MATHS.

A06.015 to A06.019 are "Spares"

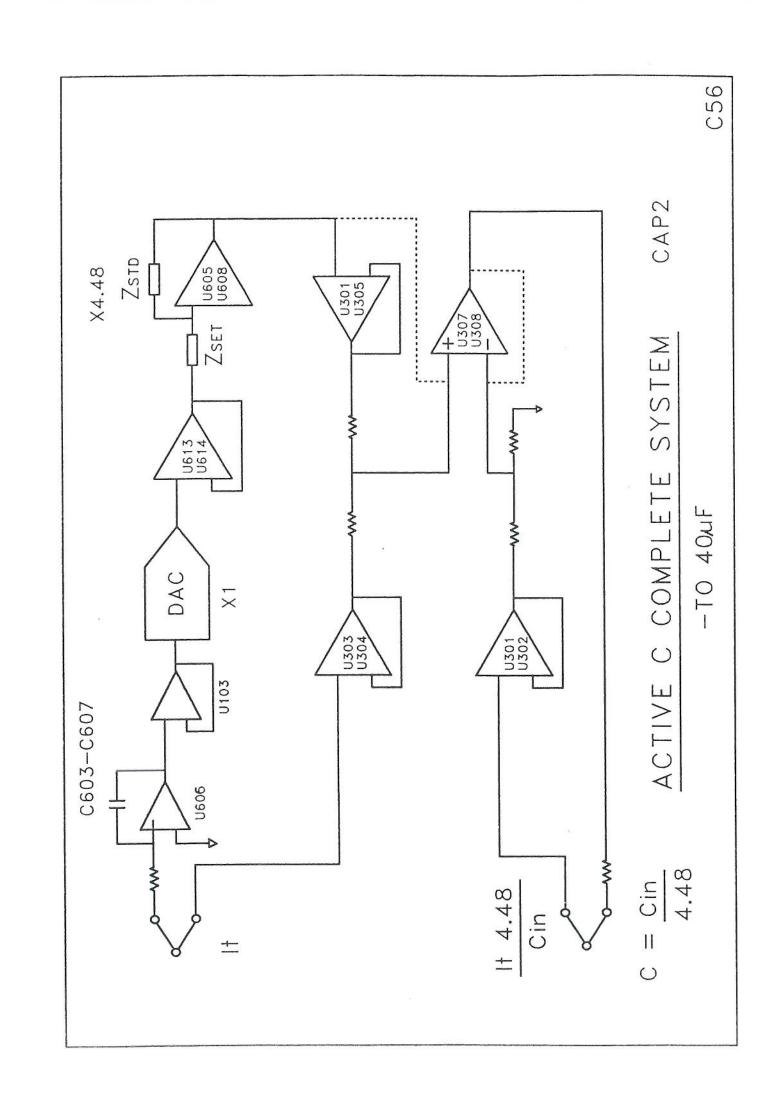

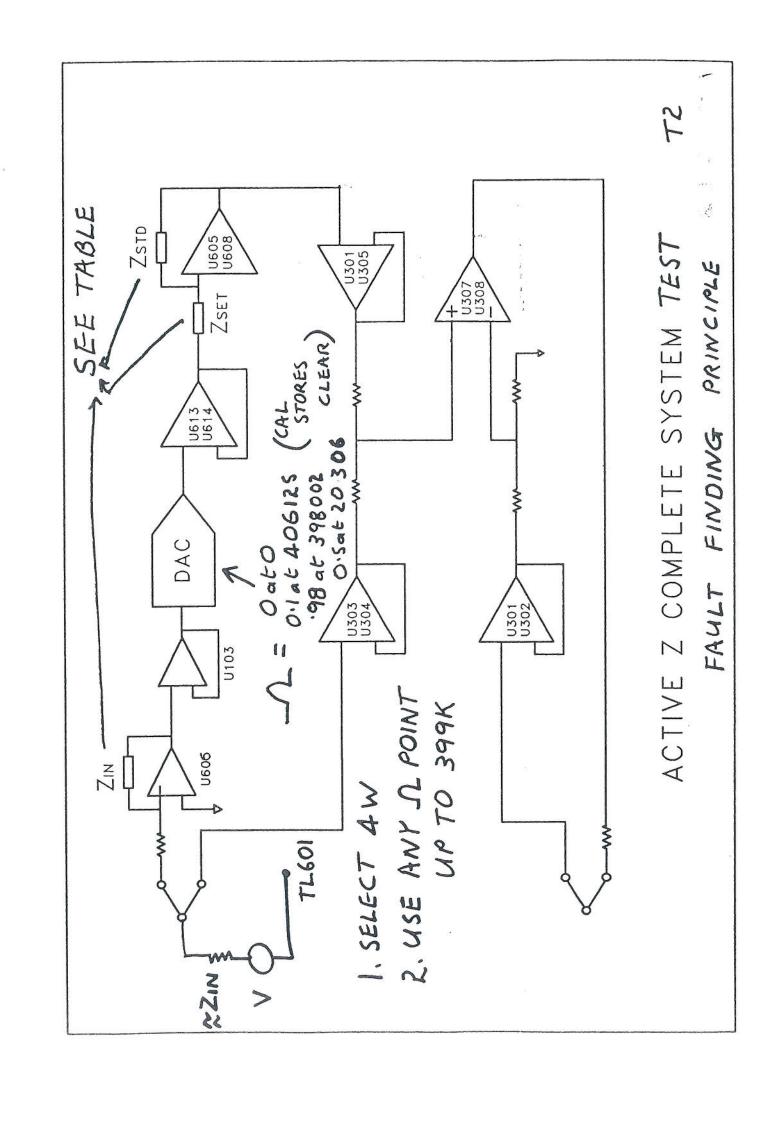

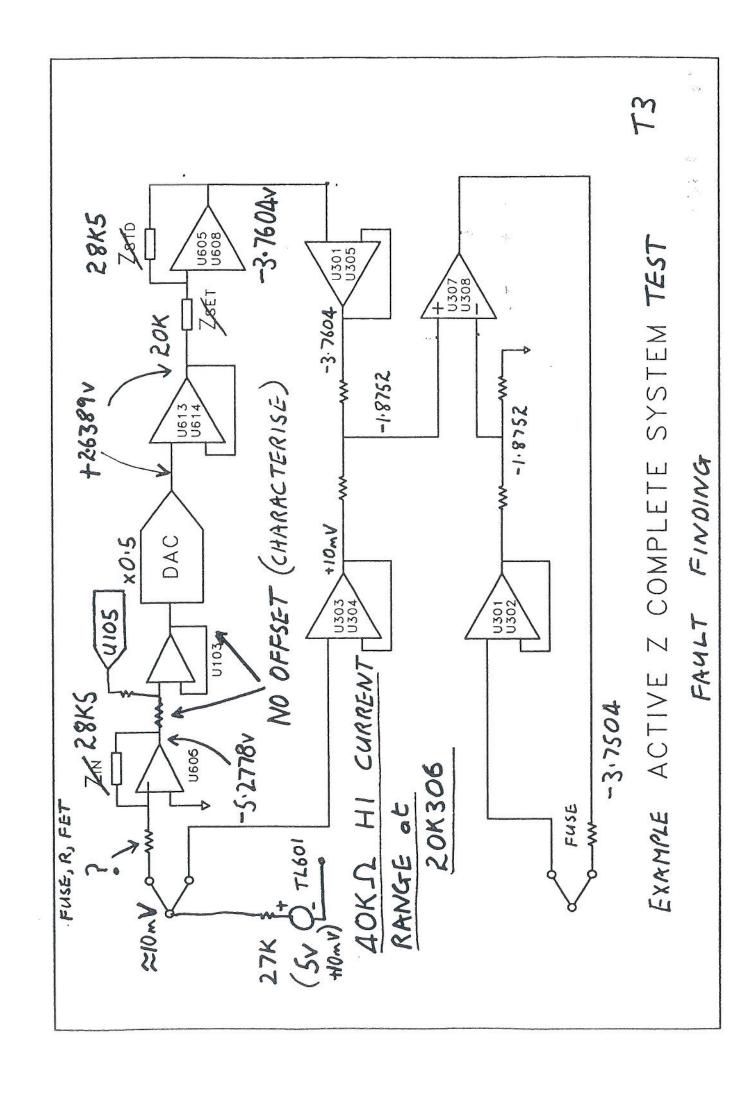

### A06.020 to A06.024 - Capacitance Tests

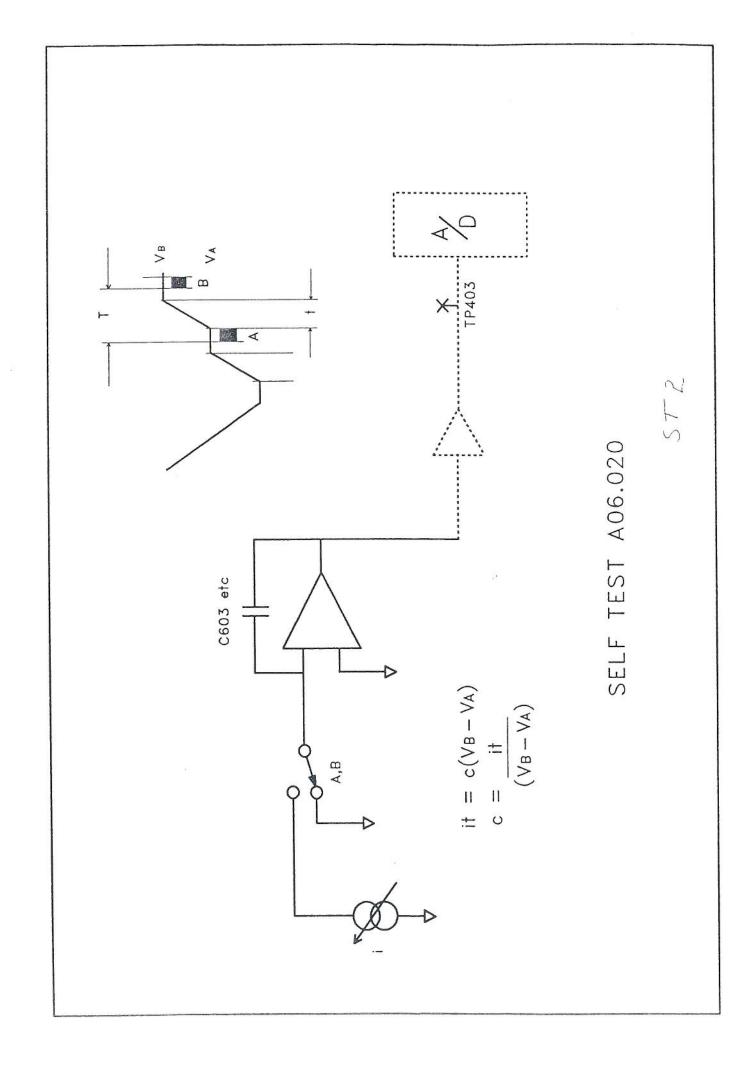

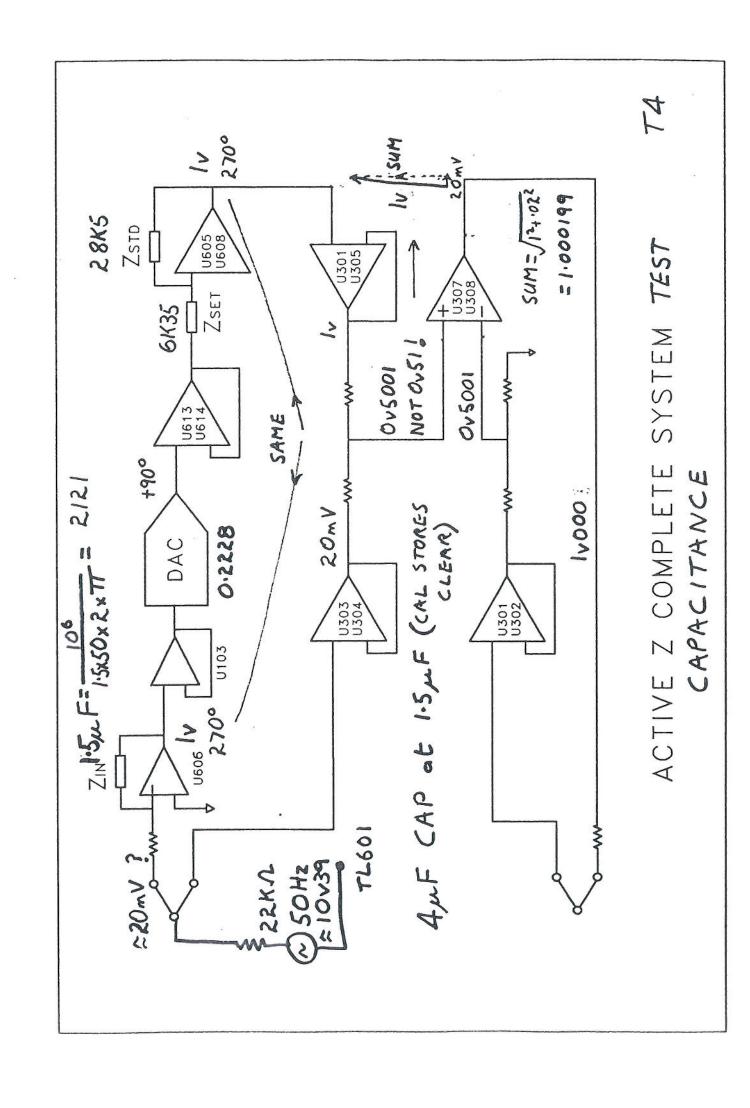

These tests all force TP607 to the negative rail. A current is then applied and removed to bring TP607 to a linear region (Measurement A). A current is then applied and removed to further charge the capacitor under test (Measurement B). (B-A) gives the voltage change on the capacitor due to I x t (current multiplied by time). From CV=It the value of C is known in Self Cal. In Self Test we just utilise the voltage change B-A. To see the waveforms use a digital scope and the REPEAT TEST button. See ST2 for sketch of a typical waveform on TP607.

| Test               | Input<br>'Curtickle'' | Time  | =Vcap<br>(TP607) | to<br>A/D (TP403) | TP403 Finishes at Nominally | C under test |

|--------------------|-----------------------|-------|------------------|-------------------|-----------------------------|--------------|

| <b>A</b> 06 020    | -144nA                | 0.1s  | 7.868            | 1.574             | -0.94                       | C603         |

| A06.020<br>A06.021 | 1.44µA                | 0.1s  | 8.52             | 1.7               | -1.2                        | C604         |

| A06.022            | 1.964μΑ               | 0.5s  | 6.68             | 1.3345            | -0.43                       | C605         |

| A06.023            | 19.2μΑ                | 0.5s  | 6.4              | 1.3375            | -0.46                       | C606         |

| A06.024            | 207μΑ                 | 0.3s  | 6.22             | 1.245             | -0.4                        | C607         |

| A06.025            | Does not e            | exist |                  |                   |                             |              |

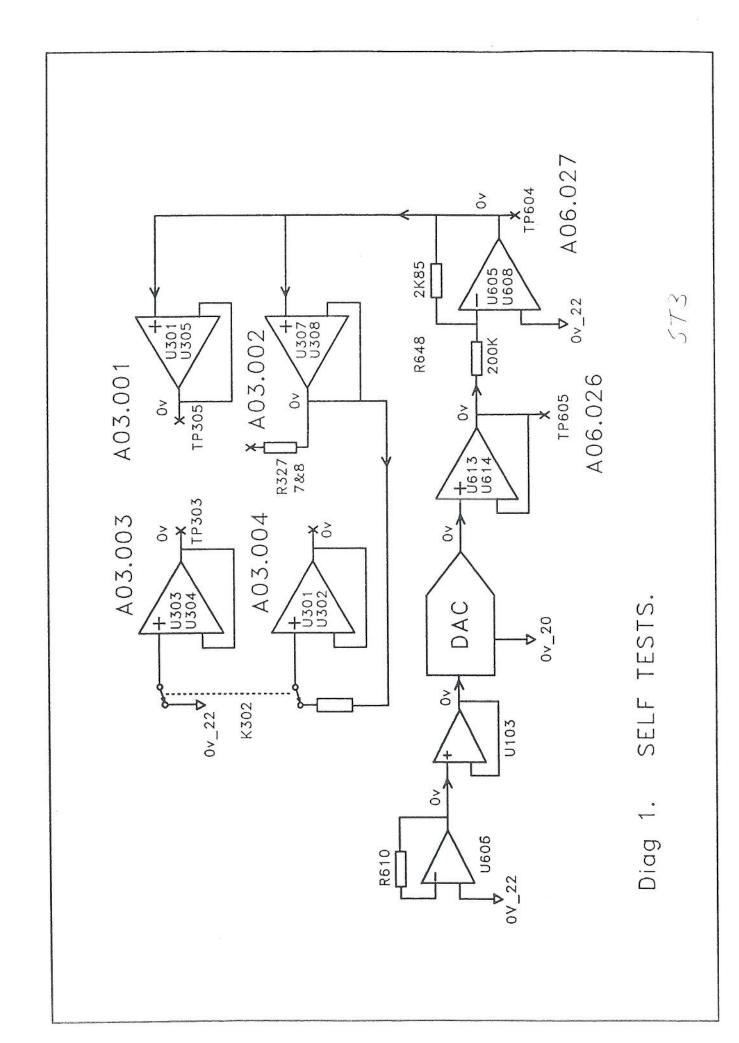

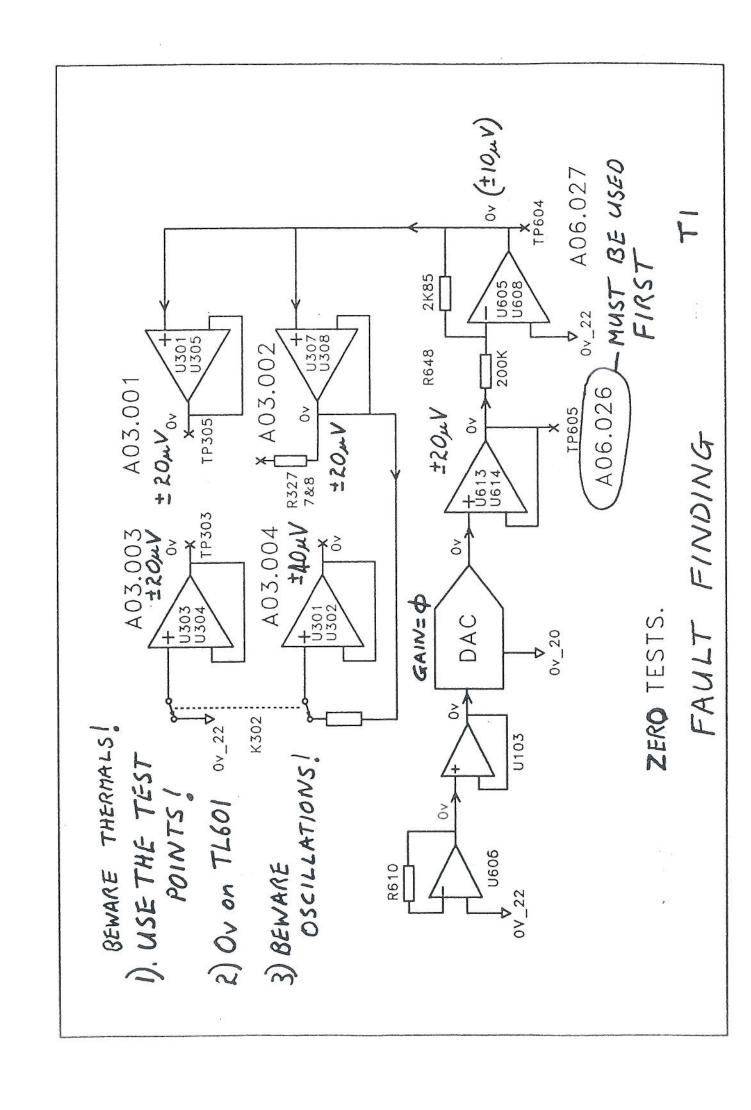

### A06.026 - A03.004

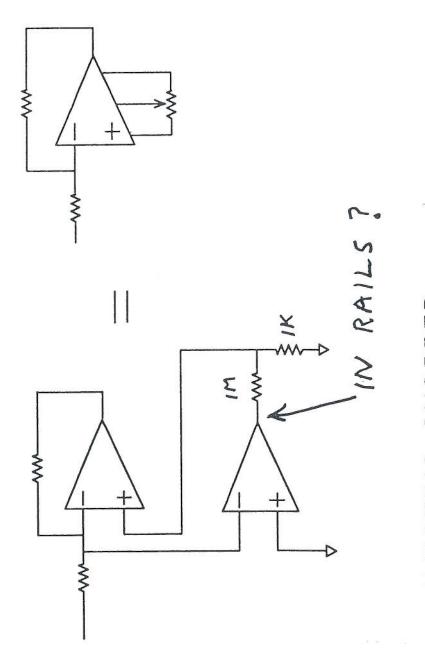

These tests check a series of composite amplifiers, most of which are followers, U608 + U605 being the only exceptions. The main DAC is forced to zero gain and the resulting outputs are measured as a "gross failure" check. The MATHS facility is used to establish the real offset of each amplifier.

Diagram 2 is a sketch of the chain to indicate the signal paths and pick-off points for each test.

| Test    | Amps offset               | Picked Off At |

|---------|---------------------------|---------------|

| A06.026 | U613+U614+DAC             | TT605         |

| A06.027 | U605+U608                 | HI_IMP_OUT    |

| A03.001 | U301+U305+A06.027         | TT304         |

| A03.002 | U307+U308+A06.027         | TT302         |

| A03.003 | U303+U304                 | TT303         |

| A03.004 | U301+U302+A03.002+A06.027 | TT301         |

|         |                           |               |

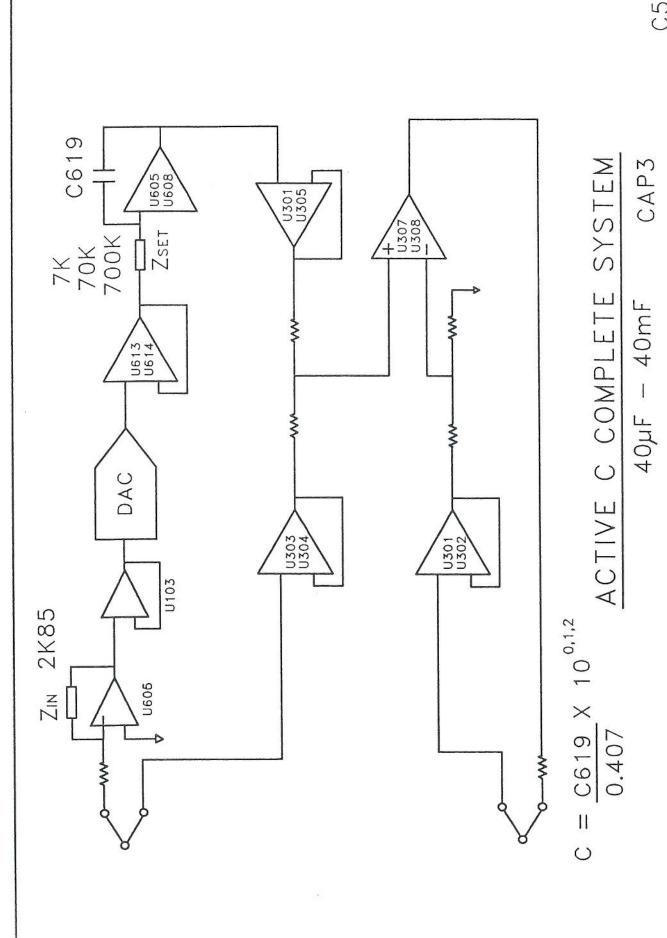

### A06.028 - A06.033

After test A03.004 we are certain that the preamp U606 can swing  $\pm 10V$  and that all other amplifiers are probably working as they have a good zero. It remains to check that all gains subsequent to the preamp are within limits. DC paths are used to check Ohms gain, but this is unfortunately not possible for capacitance gains, and we have to resort to the ramping technique used previously.

All tests go -/+ve on TP607.

| Test       | Checks                          | Vp/p          | Vp/p on           | V Final on TP403         |

|------------|---------------------------------|---------------|-------------------|--------------------------|

| A06.028    | Establish preamp span           | 12.45         | TP607             | +1.245                   |

| A06.029    | R648 28k5/20k                   | 17.74         | TP604             | -1.77                    |

|            |                                 |               |                   |                          |

| At this po | int 3 tests are inserted to che | eck followers | s for swing capab | ility. Setup as A06.029. |

| A03.005 | U301/U305 | 17.74 | TP305 | -1.77 |

|---------|-----------|-------|-------|-------|

| A03.006 | U307/U308 | 17.74 | TP302 | -1.77 |

| A03 007 | U301/U302 | 17.74 | TP301 | -1.77 |

| Test    | Checks         | Vp/p | Vp/p on | V Final at TP403 |

|---------|----------------|------|---------|------------------|

| A06.030 | R648 28k5/200k | 1.77 | TP604   | -177mV           |

| A06.031 | R648 2k85/20k  | 1.77 | TP604   | -177mV           |

| A06.032 | R648 285k/200k | 17.7 | TP604   | -1.77            |

| A06.033 | R648 6k35/28k5 | 6.68 | TP604   | -0.4             |

Test A06.033 is similar to A06.022. The DAC exactly compensates for the gain in R648 of 285k5 / 6k35 and is set to 6.35 / 28.5 or 0.222807.

Both the DAC and U605/U608 invert so the waveform on TP604 is exactly the same as on TP607.

### A06.034 to A06.036

Tests A06.034 to A06.036 check R648 700k, 70k, 7k respectively. The same remarks apply which introduced checks A06.020 to A06.024.

| Test    | Input "Curtickle" | Volts<br>TP607 | R648 | Current<br>C619 | Time  | (B-A)<br>Volts<br>C619 | TP403<br>(B-A)<br>Volts | TP403<br>Ends at. |

|---------|-------------------|----------------|------|-----------------|-------|------------------------|-------------------------|-------------------|

| A06.034 | 24μΑ              | 6.84           | 700k | 0.977μΑ         | 1.13s | -1.08                  | +0.22                   | +2V               |

| A06.035 | 24μΑ              | 6.84           | 70k  | $9.77\mu A$     | 0.5s  | -4.88                  | +0.977                  | +0.25             |

| A06.036 | i 12.05μA         | 3.42           | 7k   | 48.85µA         | 0.1s  | -4.91                  | +0.981                  | +0.25             |

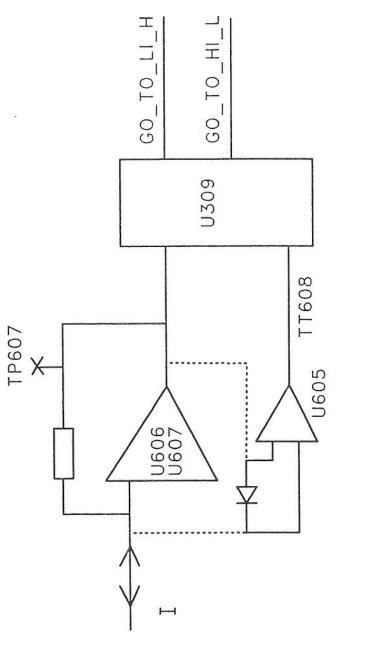

### A03.011 to A03.018

It is now required to check the error lines GO\_TO\_LI\_H and GO\_TO\_HI\_L in all possible states. The test setup is exactly as A06.006 except that the input volts (and hence TP607) are raised.

| Test    | TP607 | GO_TO_LI_H | GO_TO_HI_L |

|---------|-------|------------|------------|

| A03.011 | >10V  | 0          | 0          |

| A03.012 | 10V   | 0          | 1          |

| A03.013 | 1.0V  | 0          | 1          |

| A03.014 | 0.4V  | 1          | 1          |

| A03.015 | -0.4V | 1          | 1          |

| A03.016 | -1.0V | 0          | 1          |

| A03.017 | -10V  | 0          | 1          |

| A03.018 | <-10V | 0          | 0          |

Note:- 1 = +5V, 0 = 0V

Note that the input HI\_CLAMP comes from the middle of the clamp circuit and a fault in this will cause failure(s) in these tests. (LO\_CLAMP is direct from TP607). It is the correct operation of the clamp circuit which causes HI\_CLAMP to exceed "one diode drop" and hence change GO-TO HI L. There are no A/D measurements in the above tests.

### A06.041

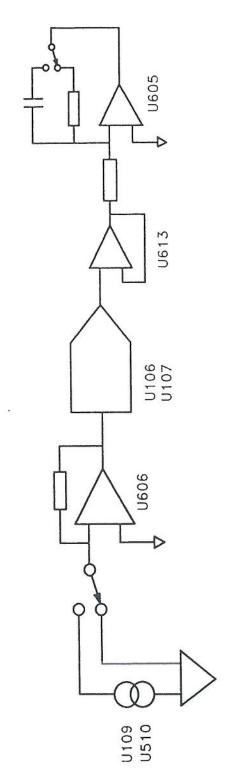

Test A06.041 repeats the setup of A03.011 and A03.018, but U605/7 is monitored via TT608. This is the output of the clamp circuit. The limits are set very wide, but typically expect 1.0 to 1.4 volts to be indicated as a result on the display. The input to U605 is a  $\pm 0.7v$  in turn seen across D609 and D610 when the clamp conducts, and this has a gain of 1 to the A/D input TP403.

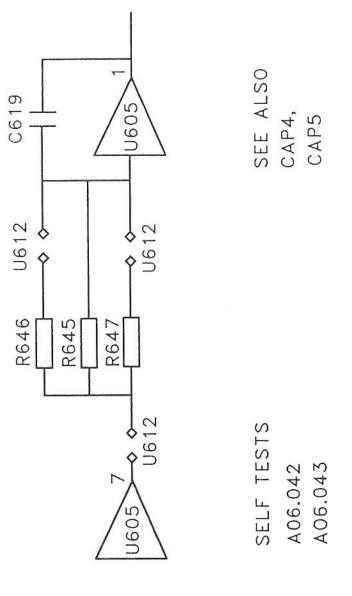

### A06.042-A06.043

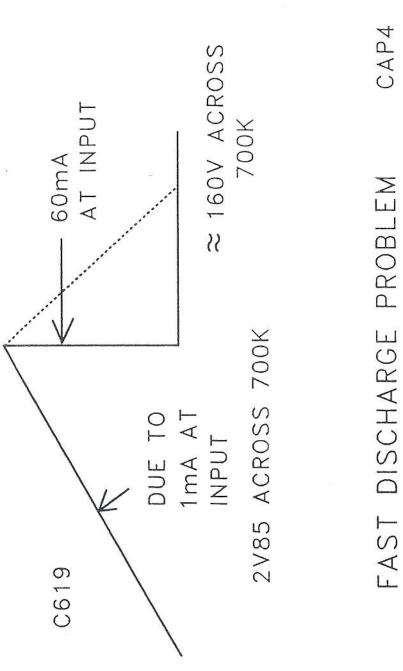

Tests A06.042 and A06.043 use the output of U605 as in test A06.041 above. This output was originally used to discharge C619 via R647, R646 and R645 in  $400\mu F$ , 4mF and 40mF ranges. We can only test the first two, as the 40mF takes far too long to attain an accurate result. The waveforms are similar to those described in the introduction to A06.020 to A06.024. The input to U605/7 is obtained by making the clamp circuit Q606, Q607 etc conduct, with TP607 at more than  $\pm 10v$ .

| Test    | Resistor | I Nominal | Time   | (A-B)<br>on TP604 | (A-B)<br>on TP403 |

|---------|----------|-----------|--------|-------------------|-------------------|

| A06.042 | R647     | 60μΑ      | 0.5sec | 3.0               | 0.6               |

| A06.043 | R646     | 12μΑ      | 1.0sec | 1.2               | 0.24              |

### MATHS TESTS

| Test    | Source          | Limits        | Possible Fault if Fail                  |

|---------|-----------------|---------------|-----------------------------------------|

|         |                 |               | 1970FT 5905 85 50 SSSSS-20 MR           |

| A06.M01 | A06.007+A06.006 | $0\pm0.0027$  | Clamp Serious Level Fault               |

| A06.M02 | A06.009+A06.008 | $0\pm0.002$   | R611+R672 Fault                         |

| A06.M03 | A06.010+A06.011 | $0\pm0.002$   | R668 Fault + R611 & R672                |

| A06.M04 | A06.013+A06.012 | $0\pm0.006$   | R668 Fault, R611 + R672, Ground Offset, |

|         |                 |               | U105 Non Linearity. (Note 1)            |

| A06.M05 | A06.014-A06.001 | $0\pm0.0057$  | U606, U607 Q611, Q613, Q602, Q604,      |

|         |                 |               | Q614 Ibias or Igate                     |

| A06.M06 | A06.026-A06.001 | $0\pm0.0004$  | OFFSET U613/U614 (Note 2)               |

| A06.M07 | A06.027-A06.026 | $0\pm0.0004$  | OFFSET U605/U608                        |

| A03.M01 | A3.001-A06.001  | $0\pm0.00015$ | OFFSET U307/U308                        |

| A03.M02 | A3.002-A06.027  | $0\pm0.00015$ | OFFSET U301/U305                        |

| A03.M03 | A3.003-A06.001  | $0\pm0.00020$ | OFFSET U303/U304                        |

| A03.M04 | A3.004-A03.001  | $0\pm0.0001$  | OFFSET U302/U301 (Note 3)               |

| A06.M08 | A06.029/A06.030 | $10\pm0.03$   | R648 20k/200k RATIO (Note 4)            |

| A06.M04 | A06.029/A06.031 | $10\pm0.03$   | R648 28k5/2k85 RATIO                    |

| A06.M10 | A06.029/A06.032 | 1±0.004       | R648 285k/28k5 RATIO (Note 5)           |

| A06.M11 | A06.042/A06.043 | 2.75+1.5-0.75 | CAP DISCHARGE RATE - U605 etc           |

|         |                 |               | R647, R646                              |

### NOTES:-

1. U105 can give unequal ± o/p at these low levels. A swap with U107 can help. Early boards had U105/2 to ST401. This was changed by ECO to ST402. A 'cut and link' is required.

- 2. Serious ground current errors can cause failures check 0V\_20 WRT 0V\_22A.

- 3. Very early models require an ECO to join K302/9 to 0V\_22 and K302/2 to RGC\_P\_NEG via 100k.

- 4. Switch errors can also cause faults an O/C drive is most likely.

- 5. If A06.M08 fails, this test will fail as well.

- 6. Note factory limits are usually 0.75 x Nominal and customer limits are 2 x Nominal.

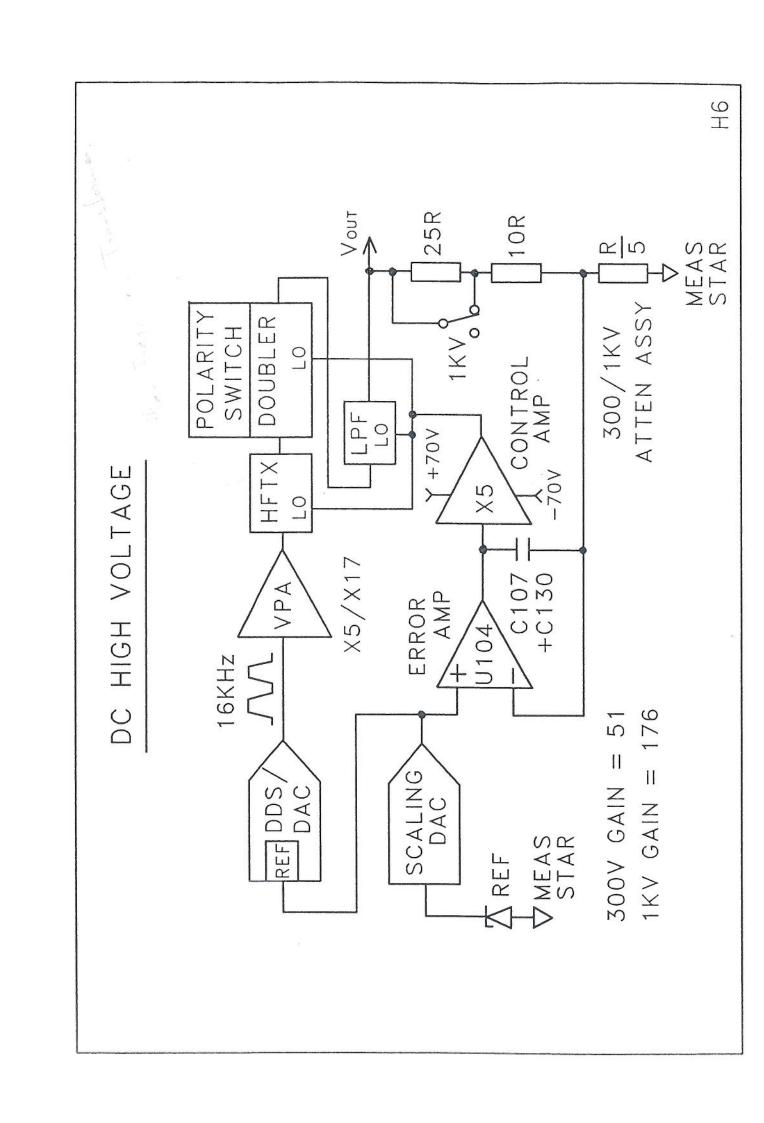

### HIGH VOLTAGE OUTPUT.

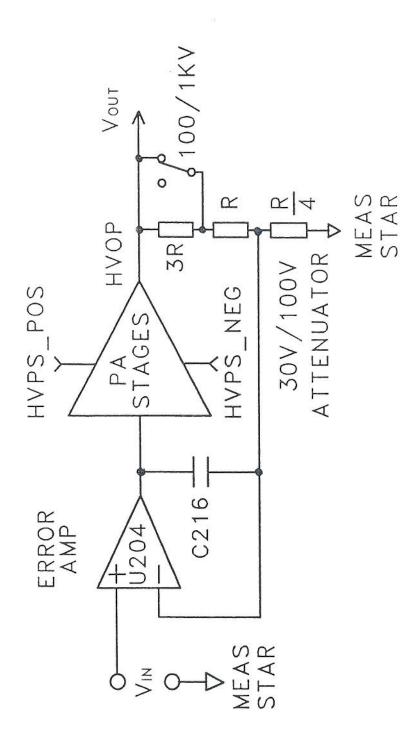

All output voltages greater than 3.2V ac/dc are produced by amplification of DAC output signals on the power pcb. ALL range amplifiers are non-inverting.

### 30V AC/DC (401096 sht 2 & 401097 sht 9)

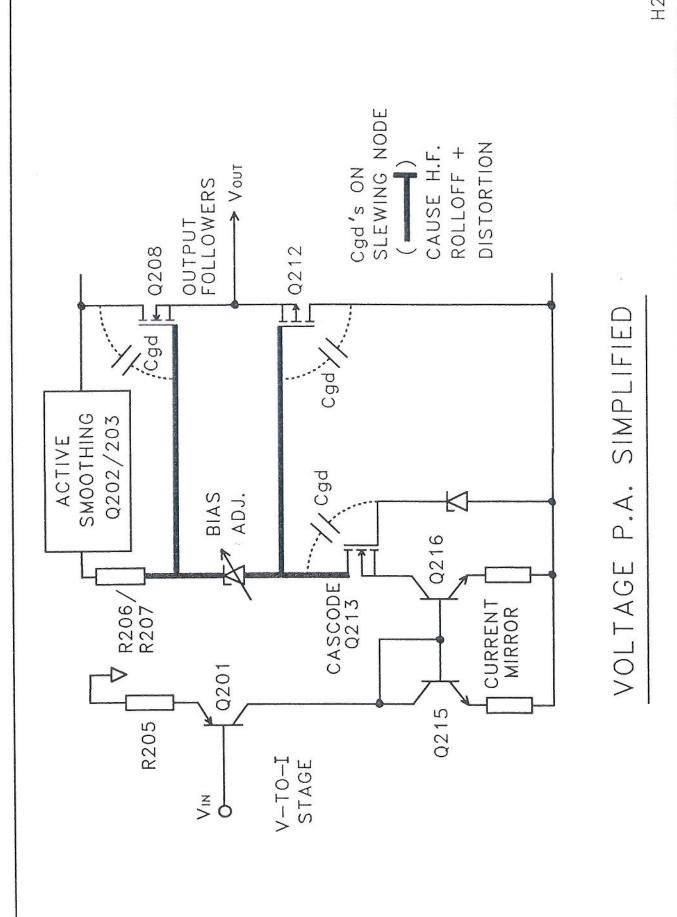

These ranges are produced by x5 amplification of the DAC\_OUT\_1 signal from the main DAC. It is input via U901 (analog) on the HV\_IP net. The attenuator R247 defines the performance of the 30V amplifier and sufficient precision is obtained without any additional measurement loops. In 30V ac/dc ranges, the voltage amplifier main power supplies HV\_PS\_POS and HV\_PS\_NEG are at +/-70V respectively (unregulated). Discrete stages Q201 through Q212 form the actual amplifying stage with R247 and U204 'closing the loop' to the required gain and precision.

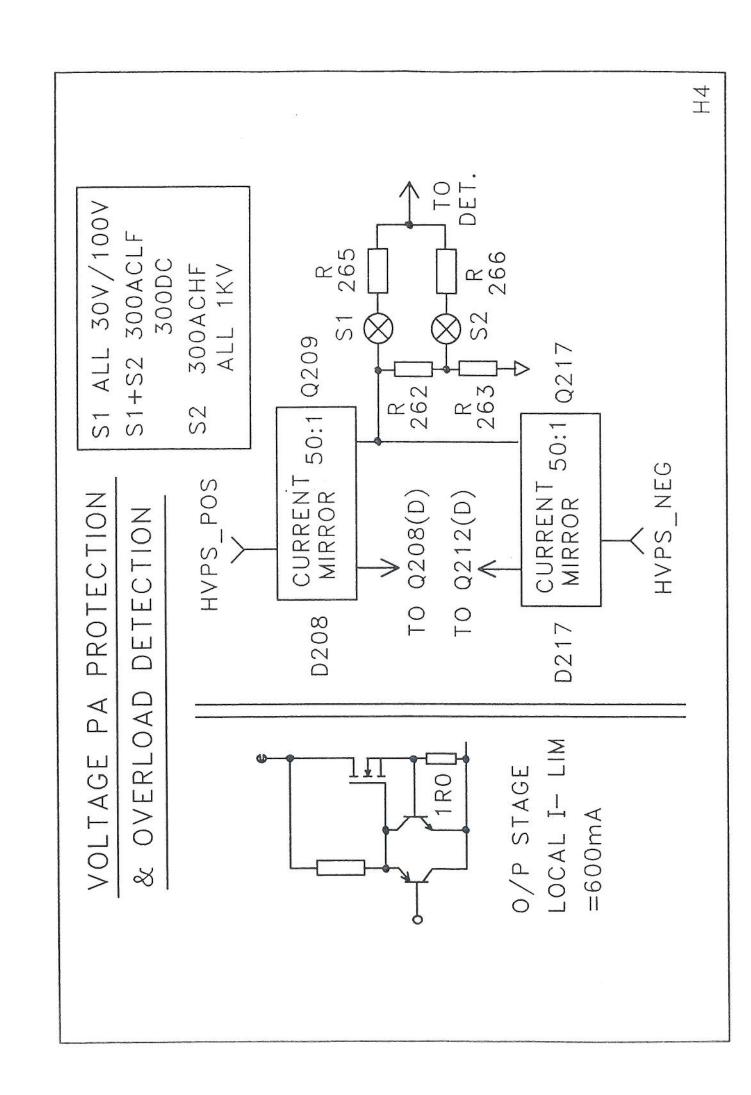

Complementary current mirrors Q209/Q217 mirror the current in the output devices, and thus the voltage developed across R262 & R263 is a measure of output current. U206/R265/R266 provide three discrete levels of overload detection for various ranges. For 30V ac/dc the detector is at its most sensitive setting (upper switch of U206 ON).

When not in use, the discrete stages are disabled by turning off the V/I stage Q201 (and thus all following stages). This is done by taking U204-3 to  $\pm 15V$  with HV\_IP\_ON\_H.

The output devices are biassed to class A/B by the U205/Q205 shunt regulator, temperature compensated by Q204 (mounted on h/s in close proximity to output devices). Bias is set by demanding 3.3VAC/1kHz and adjusting R208 for 240mVDC across R218 with no external load. This must be verified before any further fault-finding is attempted. (If set too low, oscillation will occur due to loss of bandwidth in output followers. Too high and output capability will be reduced and in extreme cases may result in thermal runaway of output devices).

Q202/Q203/C209 form an 'active smoothing' circuit for the cascode amplifier stage positive supply. This stage has no rejection whatsoever to noise/ripple present at the 'cold' end of its load resistor, so a clean supply is essential.

Q208/Q212 are protected in the short term by Q207/Q211 which limit drain current to approx. 600mA peak.

### 100V AC (401096 sht 2)

30V description applies except:-

- a) HV amp PSU raised to +/-200V (protected).

- b) Gain increased from x5 to x17 (by K202).

c) Cascode stage load resistor and other biasing w/w resistors increased to suit higher supplies (by K201).

Again , sufficient precision is obtained without recourse to any additional measurement loops.

### 300V DC (401096 shts 1 & 2)

Basic output is produced by feeding an appropriately scaled trapezoid waveform from the DDS to the 30V amplifier input via the HV\_IP net. The VPA is configured as for the 30V range except that the overcurrent detector sensitivity is lowered (both U206 switches ON).

The amplified trapezoid is ac-coupled to the HFTX primary, the secondary driving a diode voltage doubler/filter arrangement with built-in polarity switching.

Having produced the basic output power at approximately the right level, (this open-loop gain is trimmable via an FSV on the analog pcb.), an outer loop is used to fine trim the output to req'd ppm levels. The 300V/1kV attenuator assy sits between doubler output and ground, and in the 300V range has a ratio of 51:1. Output of the attenuator is compared to the DAC\_OUT\_1 signal in error integrator U104. U104 output is amplified by approx x5 in the control amplifier and used to 'tweak' the earthy end of the floating voltage doubler to close the loop.

The control amp input is monitored for overdrive (indicating loss of feedback in the loop). Excessive corrections trigger the overcurrent 'etector via D119/D120 and the CA\_OVDRV net.

### 1kV DC (401096 shts 1 & 2)

As 300V DC except:-

- a) PA configured as for 100V AC wrt gain, power supplies, and biasing components.

- b) Overcurrent detector to least sensitive level. (U206 lower switch ON).

- c) Attenuator assy ratio changes to 176:1 (by K109).

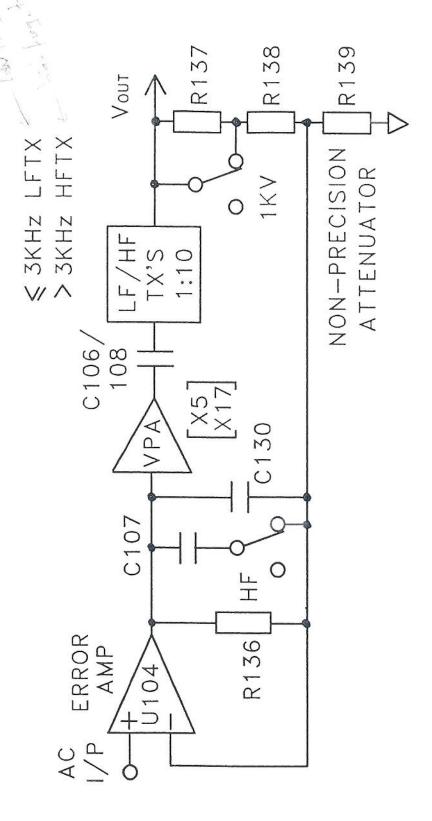

### 300V AC (401096 shts 1 & 2)

Here the 30V amp is used via one of two 1:10 step-up transformers. The LFTX T101 is used for 40Hz to 3kHz outputs and the HFTX for frequencies higher than 3kHz (max = 30kHz). Since the transformers have significant performance imperfections, a non-precision feedback loop consisting of R137/R138/R139 attenuator and error amp U104 is used to reduce the effects of:-

- a) Distortion due to core effects @ low freq end of each transformers span.

- b) Flatness errors-these are substantial with the LFTX in particular due to resonances.

- c) Output Z effects. These again are large with the LFTX due to high winding resistance and leakage inductance.

The gain of this inner loop is approx 11 and is set by R136/R139. Output/input gain is approx 51:1, set by R138/R139.

Overcurrent detector sensitivity is medium (both switches of U206 ON) for LF freqs and low (U206 lower switch ON) for HF freqs.

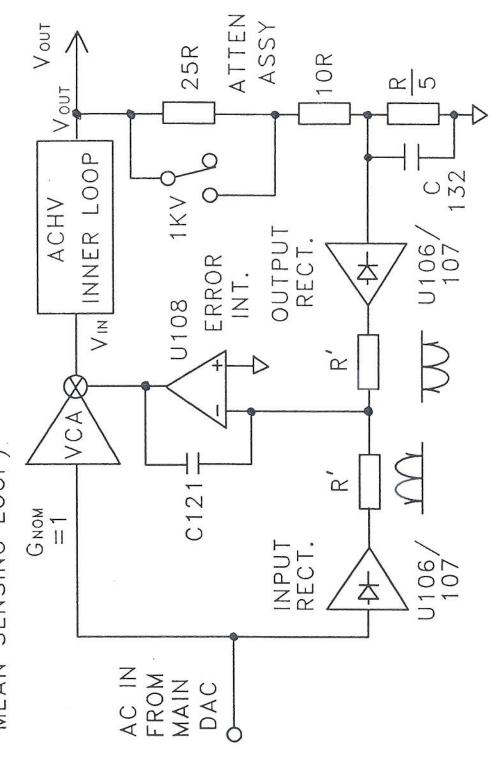

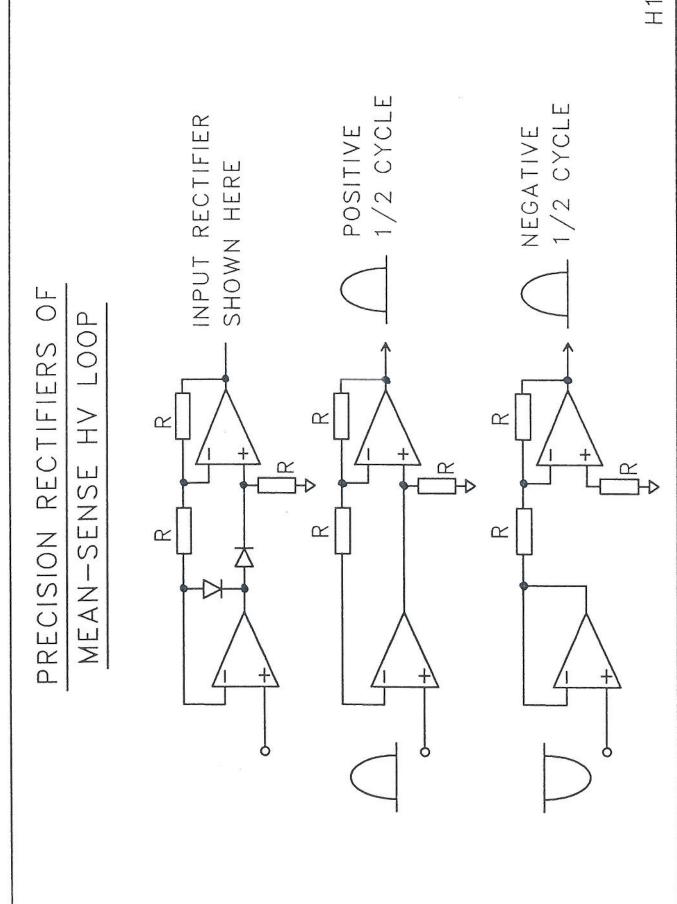

The inner feedback loop still does not provide the necessary precision so a further outer control loop with high gain is required to performance to ppm levels. This works by comparing the output from the 300V/1kV precision attenuator assy (51:1) with the AC reference input DAC\_OUT\_1. This is achieved by complementary matched precision rectification of both input signal and attenuated output. The rectifier outputs are summed and integrated in U108 to control a varible gain buffer U109 so as to bring the two signals to the same mean amplitude, thus control loop and stabilising the gain of the system to ppm. closing the levels. Performance of this system relies heavily on signal purity as regards the input signal since the loop is vulnerable to mean-sense These impact on flatness, particularly around 1.5 to 3kHz. this reason, flatness spec tends to be wider than 30/100V AC ranges.

### 1kV AC (401096 shts 1 & 2)

As 300V AC except:-

- a) PA config'd as for 100V AC wrt gain, power supplies & biasing components.

- b) Overcurrent det to lowest sensitivity (U206 lower switch ON) for all freqs.

- c) Attenuator assy & inner non-precision attenuator both change to 176:1 (by K109).

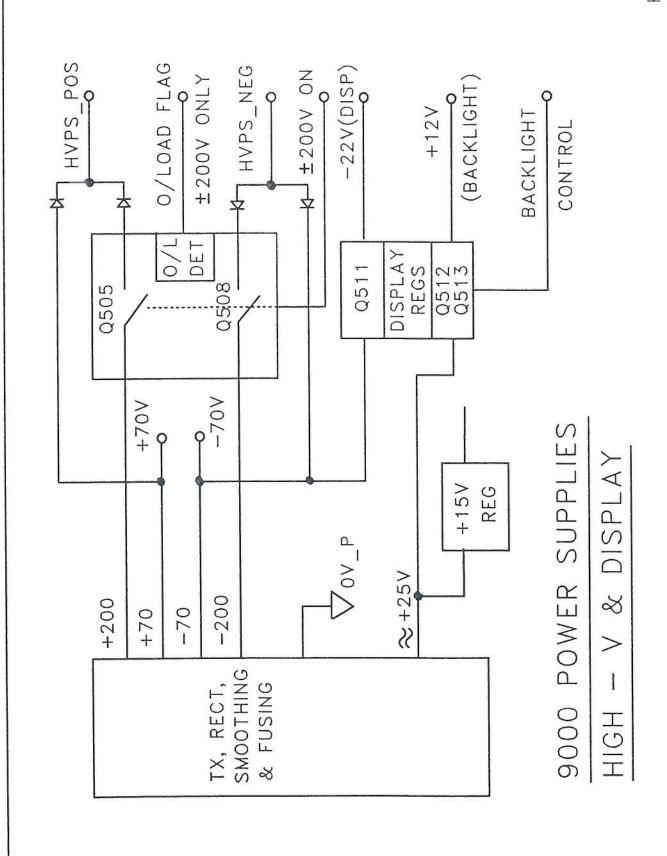

### +/-70/200V PSU switch and Display PSUs (401096 sht 5)

Power mosfets Q505/Q508 are fully enhanced when the HV\_PS\_ON\_H line is taken high to raise the normally +/-70V supplies to +/-200V. Average drain currents are monitored by Q503/Q506 and an error flag HV\_PS\_OL\_L is produced if either exceeds approx 200mA. Software then removes the enabling signal and forces neutral state. The +/-70V supplies are not monitored for overcurrent.

+/-70V and +/-200V (switched by Q505/Q508) are diode-ORed to produc the PA supplies HV\_PS\_POS and HV\_PS\_NEG.

Q511 circuit produces -22V regulated from the -70V rail to power the display (not overcurrent protected).

Q512 circuit produces +12V regulated for the display backlight inverter. It can be shutdown for standby by LCD\_BL\_ON\_L going high. The +12V supply is not overcurrent protected.

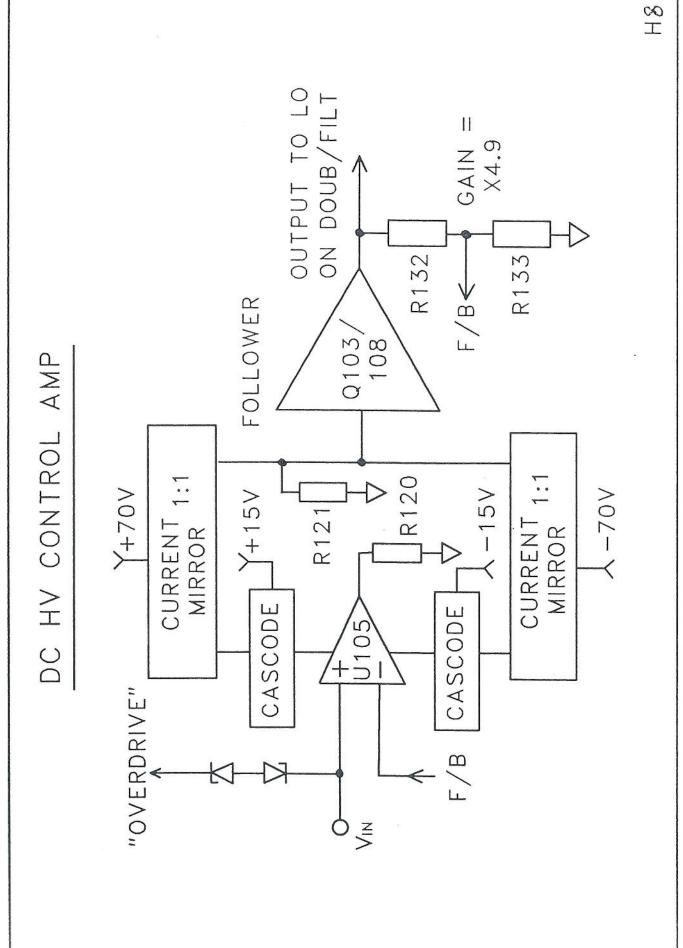

### DC HV Control Amp (401096 sht 1)

This block operates from +/-70V supplies and when not in use has its input grounded via R119. When the input of U105 is driven, The load resistor on U105 output causes differentials in the supply rails to the op-amp. These currents pass to mirrors on the +/-70V rails (via cascodes Q101/Q105). Mirror ratios are 1:1 and the output voltage is developed across R121, to be buffered by Q103/Q108 which are in turn biassed into class A/B by D107/D108. Gain of this discrete section is approx 4.

Overall feedback is applied to U105 inverting input via R132/R133 to set the closed-loop gain to approx 4.9.

A degree of protection is provided by ballast resistors R115/R127 in the +/-70V rails.

### LF Pulse Range (401096 sht 2 & 401097 sht 9)

For pulse outputs at freqs of 1kHz and lower, and peak amplitude of more than +/-6V, the pulse system output is routed via U901 (analog) to the 30V amplifier before passing to the output. Configuration is identical to 30V AC/DC cases and up to 60V ptp is available.

R201/C244 slow the fast edges from the pulse output stage to prevent overshoot and ringing of the PA.

# HIGH VOLTAGE & POWER SUPPLIES SELF-TEST DESCRIPTION

P05.001 - Tests +5V PSU via R546. Inst state = NEUTRAL. P05.002 - Tests +15V PSU via R541. Inst state = NEUTRAL. " -15V " " " P05.003 -\_\_\_\_\_ P05.004/P05.005 - Tests high-I +/-7.5V supplies via R546. P05.006 - Tests -22V PSU via R545. Inst state = NEUTRAL. \_\_\_\_\_ " +70V " P05.007 -\* R532/R533/R534. Inst state = NEUTRAL. \_\_\_\_\_ P05.008 --70V \* \* R535/R536/R537. \_\_\_\_\_ P05.009 -" +200V " \* R532/R533/R534. Inst state = NEUTRAL except:a) HV\_PS\_ON\_H is taken HIGH (to enable +/-200V). \_\_\_\_\_ b) Relay K202 is energised (to protect R247). P05.010 - Tests -200V PSU via R535/R536/R537. Inst state = as for P05.009. \_\_\_\_\_ P02.001 - Tests 30Vamp positive swing via R250/R251 - main DAC = +FS. \_\_\_\_\_ P02.002 zero output " = ZERO. -----P02.003 -\* = -FS. negative swing \* ----inverting input with main DAC = ZERO. P02.004 -\_\_\_\_\_ NOTE - The following tests involve 100V/300V/1kV operation. Remember there is no warning beeper in self-test mode. P02.005 - As P02.001 except PA config'd for 100V AC range. To prevent

overstressing of w/w resistors in PA, pathway exists only for

\_\_\_\_\_

duration of test.

P02.007 - As P02.005 except main DAC = -FS.

PO2.006 - As PO2.002 except PA config'd for 100V AC range.

P02.008 - As P02.004 except PA config'd for 100V AC range.

```

PO1.001 - Output of DC HV error amp U104 @ +FS on 300V DC range via R111

_____

and EA_TST.

PO1.002 - Output of DC HV control amp @ +FS on 300V DC range via R102/R142

and CA_TST.

P01.003 - Output of 300V DC system @ +FS via R102/R142 and VHV_AMP_TST.

P01.004 - Check inverting input of error amp U104 @ +FS via VHV_ATT_TST.

P01.005 - As P01.001 except main DAC = -FS.

_____

P01.006 - As P01.002

_____

P01.007 - As P01.003

-----

P01.008 - As P01.004

-----

P01.009 - As P01.002 except done @ +FS on 1kV DC range.

P01.010 - As P01.003

-----

P01.011 - As P01.004

P01.012 - As P01.002

" -FS "

P01.013 - As P01.003

_____

P01.014 - A5 P01.004

```

The remaining tests check that the HVAC VCA control port voltage is "within bounds", inferring locking of the outer measurement loop. (via AC\_HV\_TST).

| P01.015 - | 320V/40Hz   | P01.020 - | - 1050V/3kHz   |

|-----------|-------------|-----------|----------------|

| P01.016 - | 320V/3kHz   | P01.021   | - 1050V/3.1kHz |

| P01.017 - | 320V/3.1kHz | P01.022   | - 1050V/10kHz  |

| P01.018 - | 320V/30kHz  | P01.023 - | - 500V/20kHz   |

| P01.019 - | 1050V/40Hz  | P01.024   | - 330V/30kHz   |

### Math Tests

-----

These can only be viewed via the self-test print-out facility, and only ever appear on the screen if they fail. Even so, the constituent test results are not shown on screen, so a full printout is necessary to chase any math test failures.

The four range configurations are checked for +/-FS gain and input offset. The equations used in the math tests are given below:-

```

002.M01 - 30V amp input offset. A01.040-P02.004

P02.M02 - 30V amp gain pos. (P02.001-P02.002)/(A01.036-A01.040)

P02.M03 - 30V amp gain neg. (P02.003-P02.002)/(A01.037-A01.040)

P02.M04 - 100V amp input offset. A01.040-P02.008

P02.M05 - 100V amp gain pos. (P02.005-P02.006)/(A01.036-A01.040)

P02.M06 - 100V amp gain neg. (P02.007-P02.006)/(A01.037-A01.040)

_____

P01.M02 - 300V DC system input offset +FS. A01.036-P01.004

_____

-FS. A01.037-P01.008

P01.M03 -

_____

P01.M04 -

gain +FS. P01.003/P01.004

_____

-FS. P01.007/P01.008

701.M05 -

_____

PO1.MO6 - 1kV DC system input offset +FS. A01.038-P01.011

P01.M07 -

-FS. A01.039-P01.014

_____

P01.M08 -

gain +FS. P01.010/P01.011

_____

" -FS. P01.013/P01.014

P01.M09 -

```

### HIGH VOLTAGE - SERVICING AND FAULT FINDING

### Safety First

- a) Never work with both hands when instrument switched on. The 9000 is more dangerous than a floating source in this respect.

- b) When using self-test pathways involving high voltage configurations remember there is no warning beeper.

- c) If the PA is faulty, remove the  $\pm 1.200$ V fuses F501/F502 and work in the 30V range until the fault is cleared.

- d) When F501/F502 are fitted, there is a 3.9 second RC on the main reservoirs C501/C502. Therefore wait about 20 sec before touching PCB.

- e) Never switch on with U801 not present : relay and subsystem control lines will be undefined and a bad 'blow-up' will result.

### Connections

Remember it is not necessary to re-connect the high-current secondaries to run the high-voltage section. Slide some thin card between the PCB lugs and transformer connections. Both star points must be screwed down as must the LFTX right-hand mounting lug. This connects the core to chassis and screens the high-voltage secondary. Electrostatic coupling and oscillation may occur if core not grounded.

### Power Supplies

The display supplies (+12V & -22V) are not overcurrent protected so expect damage if these are shorted out. This usually takes out the series bass transistor and associated transzorb. The base-defining zener/diode chain may also be damaged. -22V supply damage results in blowing of the +/-70V fuses and can easily be mistaken for a PA fault. A good indication of this fault is blown +/-70V fuses and intact +/-200V fuses. Watch out for the LFTX RH mounting lug shorting to -22V track close by (especially on early units).

The +/-200V switch circuit rarely gives trouble but following any kind of PA 'blow-up' it pays to check Q505/Q508 and zeners D535/D536. Failure to do this could result in +/-200V to the PA in 30V mode which would most likely re-damage the PA. The w/w resistors and attenuator R247 would certainly be seriously overstressed by this.

### Power Amp - Common Faults

### a) Insulator Breakdown @ Q208/Q212

This was common and a serious problem on older units using 'Kapton' (yellow) insulators. These are now mica and the problem has gone away, but some very early units were shipped with the Kapton insulators. Once breakdown occurs, a short is formed and is permanent. Always replace insulators with the mica type for improved reliability. This is quite damaging if it occurs: R218/R237 go open and R220/R238 vaporise as a result. Other bits to check are Q208/Q212/Q505/Q508/D535/D536 & R219/R222/D207/D211. If either of the output mosfets are damaged, check also the driving follower and current limiter.

### b) Noisy - Gain Stepping (Worst @ 100kHz)

Caused by Q204/heatsink interface having a DC leakage, the effective resistance being high and intermittent in value. This was seen only with Kapton and should have gone away. It causes gain variation in the main cascode stage and is best looked for at the output of the OP37. Here the full magnitude of the gain change will be seen, even at LF. At the output, the effect is diminished by the loop gain of the amplifier. This is related to dirt behind the transistor rather than breakdown and has been seen in both 30V and 100V ranges.

'Value stepping' of the cascode stage w/w load resistors has also been encountered, but more rarely than the insulator problem.

50/60Hz noise will get everywhere if the active smoothing driver supply is broken, causing noise and 'beating' problems. Check with 'scope. Always look carefully for oscillations when chasing noise problems.

# C) KWV Series Wirewounds

Only fitted to engineering models. There was a reliability problem and none were shipped. To use an engineering model for demo etc, they ought to be replaced.

### d) 30V DC Offset / Linearity Problems

- 1) Check 3V range to ensure fault is with power board.

- 2) D219 to D222 leakage. Try lifting them they are only clamps.

- 3) D229/D230 leakage they can be carefully disconnected when the amplifier is ON. They prevent a relaxation oscillation which can occur when entering the range.

- 4) Leakage @ U203 or U406. U203 can be replaced and U406 unplugged.

- 5) Check for oscillation @ various levels between -32V & +32V.

- 6) Poor (resistive) connections @ main star points. Check also on

analog PCB.

- 7) R247 faulty. One unit only seen with 15ppm settling over about 20 sec to final correct value.

- 8) OP37 excessive bias current seen only once caused failure of PO2 "zero" tests.

- e) Oscillation or Thermal Runaway

- 1) Bias setting incorrect see circuit description or test proc.

- 2) Thermal runaway @ full power on 1kV ranges (trips HV power supply after about 15 mins). Seen on two engineering models only and cured by replacing 0208 & 0212.

### Inner HV Loops and Transformers

Will not turn on @ 1050V/40Hz - check transzorbs across TX primary coupling caps as there can be a few volts offset at the PA output, exacerbating transformer saturation problems. Slow ramp-ups are used on the 1kV AC range to reduce flux peaks at these lower frequencies. Ramp-down to 320.01V occurs for certain frequency changes for the same reason. Another clue to DC on the primaries is excessive core noise from the HF transformer.

Earlier units had LF transformers with higher leakage inductance. This caused peaking such that inner loop flatness error could be up to +30% at 3kHz. A large damping resistor is fitted to these units. The TX was improved and the resistor removed. If flatness problems persist around 2 to 3kHz (usually -500ppm'ish) on these older units then the TX /damping resistor mod should be done.

The inner AC HV loop may be 'opened' by shorting out R136. The DC HV doubler/filter has no history of problems.

### Outer HV Loops

The DC HV control amp has no history of problems and may be worked on in the neutral state. (The input is grounded by R119).

The AC HV precision rectifiers have seen some changes. Very early units with OP270's in U106 & U107 positions may have poor 300V/30kHz linearity (caused by marginal slew-limiting). They should be changed for he later types (AD712/OP271).

Excessive offset at either U106/U107/U108, diode leakage, or excessive op-amp bias currents will cause poor LF linearity.

The outer loop may be 'opened' by linking TL101. The VCA then runs at a nominal gain of 1.

Flatness problems due to PCB effects (hook) in the attenuator assy have been experienced with some non-approved suppliers' boards. Errors of up to +2000ppm @ 20kHz have been seen. The only fix is another assembly - the resistors can usually be reclaimed. C132 is for HF flatness compensation, and if of the wrong value can prevent calibration @ 330V/30kHz.

Remember the outer loop is dependent on signal purity from the analog board and within the amplifier. Excessive distortion or mean-sense error will have flatness implications. Serious errors in the inner loop will generally have second-order implications in the outer loop.

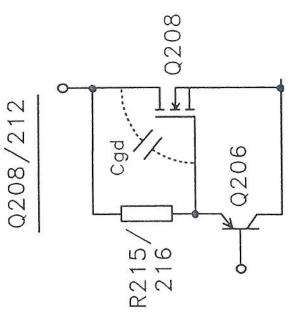

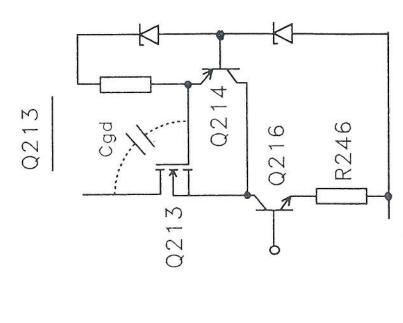

## FIXING THE Cgd PROBLEMS

EFFECTIVE INPUT CAP VERY LOW DUE TO Q206(C)&(E) FOLLOWING BASE SIGNAL

"LOST" CURRENT THRO' Cgd IS RETURNED TO Q216 BY Q214

## - CLOSING THE LOOP VOLTAGE PA

30/300V GAIN = R+R/4 = 5

(±70V)

R+3R+R/4 = 17 (±200V)R/411 100/1000V GAIN

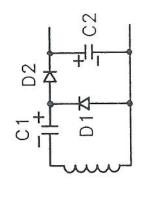

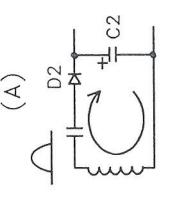

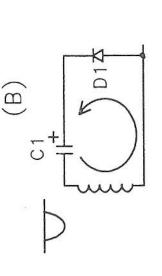

# HALF WAVE DIODE DOUBLER

TWO USED ON OPPOSITE PHASES TO GIVE FULL WAVE DOUBLING.

ON (+)VE 1/2 CYCLES C2 IS CHARGED VIA D2 (A)

ON (-)VE 1/2 CYCLES C1 IS CHARGED VIA D1 (B)

VOLTAGE DEVELOPED ACROSS C1 ON (-)VE 1/2 CYCLE ADDS TO AC SOURCE ON NEXT (+)VE 1/2 CYCLE

## ACHV INNER LOOP

- PRODUCES BASIC OUTPUT POWER FOR HVAC.

- REDUCES DISTORTION @ LOW FREQS DUE TO TX SATURATION BY VIRTUE OF LOOP GAIN. REDUCES FLATNESS ERROR OF TX'S. (2)

- (3)

## ACHV OUTER LOOP

PROVIDES FINE CONTROL OF HV GAIN TO PPM LEVELS (BY USE OF THE DCHV PRECISION ATTENUATOR IN A MEAN SENSING LOOP)

# HIGH VOLTAGE - HARDWARE OVERVIEW

| RANGE  | GAIN | HVPS       | OUTPUT CONTROL       |

|--------|------|------------|----------------------|

| 30VDC  | +5   | 10V        | NONE:DIRECT FROM P/A |

| 300VDC | +51  | +51 ±70V   | DCHV CONTROL LOOP    |

| 1KVDC  | +176 | +176 ±200V | DCHV CONTROL LOOP    |

| 30VAC  | +5   | +5 ±70V    | NONE:DIRECT FROM P/A |

| 100VAC | +17  | +17 ±200V  | NONE:DIRECT FROM P/A |

| 300VAC | +51  | +51 ±70V   | ACHV MEAN SENSE LOOP |

| 1KVAC  | +176 | +176 ±200V | ACHV MEAN SENSE LOOP |

## ERROR FLAGS

EITHER OR BOTH CAUSE A SEQUENCED SHUTDOWN TO PS OVERLOAD - ACTIVE ONLY WHEN HVPS = ±200V PA OVERLOAD - ACTIVE FOR ALL RANGES NEUTRAL STATE.

LOW CURRENT ARCHITECTURE ( \$ 320mA)

3.R SENSE PSU (TX, RECTIFIERS, SMOOTHING)  $I_0 = V_i$ D523-6 RLOAD -775 +775 RSENSE HIGH CURRENT ARCHITECTURE (>320mA) U401 Q414-32 U402 OUTPUT STAGE ERROR AMP V-I U304 U305 U308 ST301 œ 33.3m D 3R 5mD R SENSE 07\_24 V\_I\_DRV 107mV > 100mV VSENSE 1111 15 320mV 320mV VRANGE DCV/ACV RANGES ST502 300mV I RANGE 3.2A 20A

CLASS AB OUTPUT STAGE - 3MA RANGE

# GAIN DEFINING NETWORK AND INPUT CLAMP

SIMPLE NETWORK

ACTUAL NETWORK

3 8

~

$$\frac{V_0}{V_i} = \frac{R + \Delta R}{3R + \Delta R}$$

$$= \frac{1}{3} \left( 1 - \frac{2}{3} \cdot \frac{\Delta R}{R} \right)$$

IN

$$\frac{V_{i}}{3} \otimes \frac{V_{i}}{3} \otimes$$

$$\frac{V_0}{V_I} = \frac{1}{3} \cdot \frac{5}{5}R + \Delta R = \frac{1}{3}$$

R301 (8X3K3)

1 U301 🛇

2

œ

## DC STABILISATION LOOP

### GUARDING

WITHOUT GUARDING

WITH GUARDING

### CIRCUIT DESCRIPTION - POWER PCB

### **CURRENT SECTION**

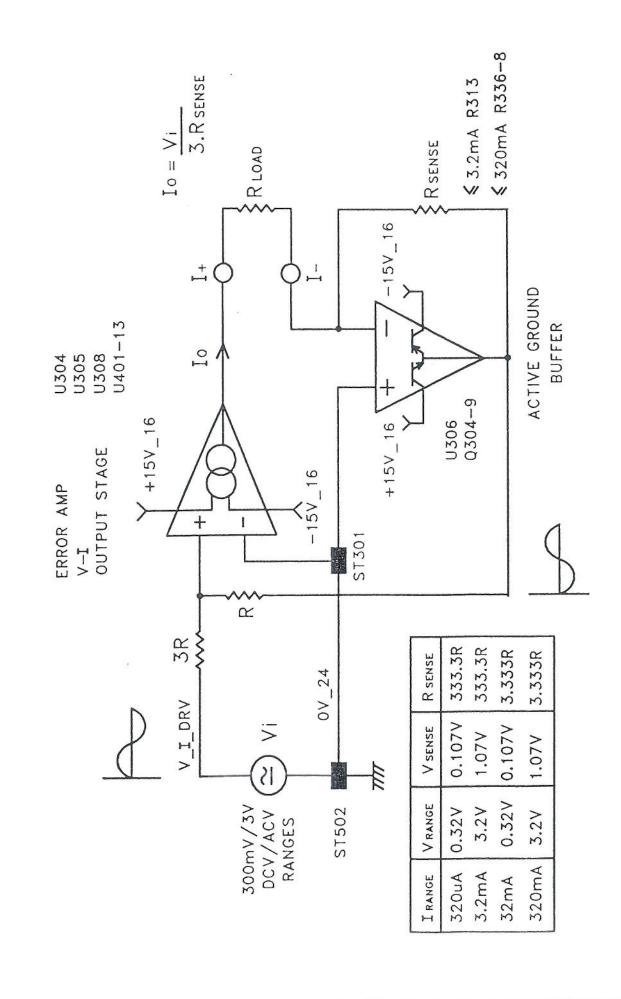

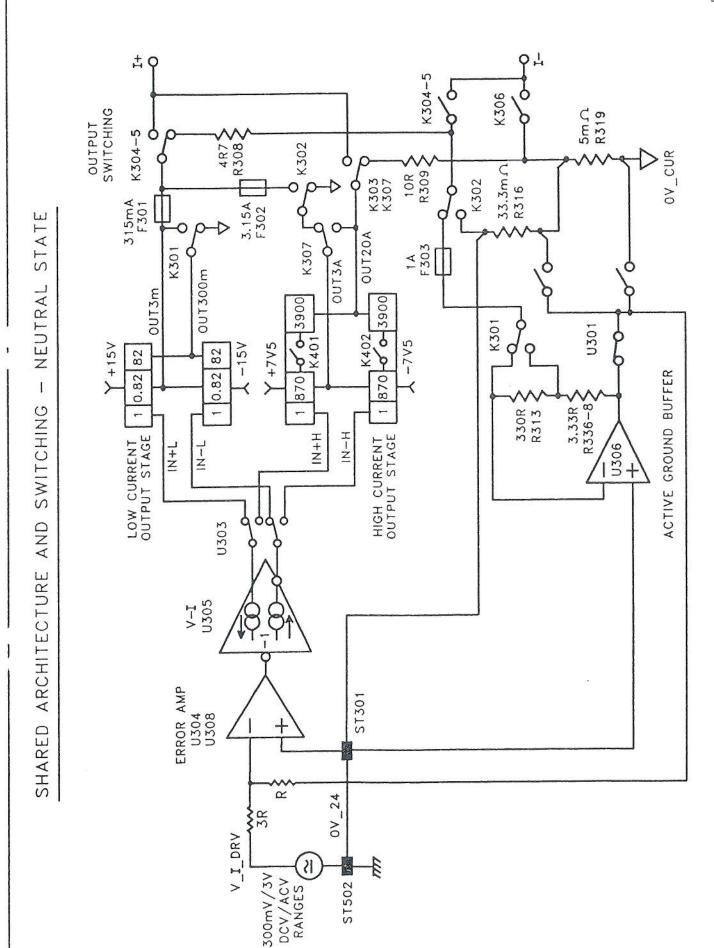

### Overall Loop (401096 Sht 3):

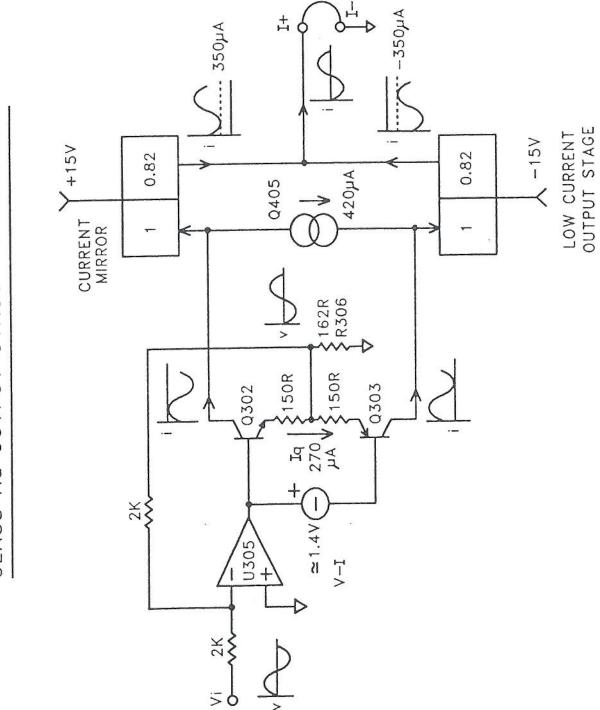

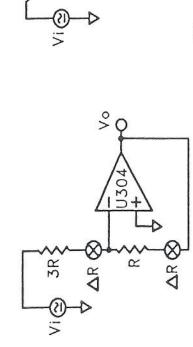

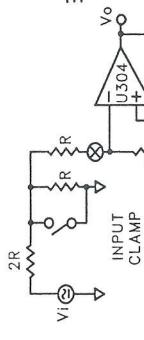

Precision current is provided by a V-I converter (transconductance amp) driven by the 300mV and the 3V voltage ranges. The output current is sensed via I-, on its return. As the I- point is held at ground potential a positive output current produces a negative voltage on the opposite end of the sense resistor (R316, 319, 313, 336-8). This sense voltage is compared to the input voltage via a feed back network (R301) at the error amp virtual earth input (U304). The error signal produced by the input amp is turned into a differential current by the small signal V-I converter (U305). This current is then amplified by the appropriate output stage.

At high currents (>0.32A) the I- end of the sense resistor is held at ground potential by both earthing the sense and by floating the output stage and its power supply. At low currents (<0.32A) the I- current is fed into the virtual earth of a ground referenced inverting amp (U306) (transresistance amp).

### • Input Network and Error Amp (401096Sht3):

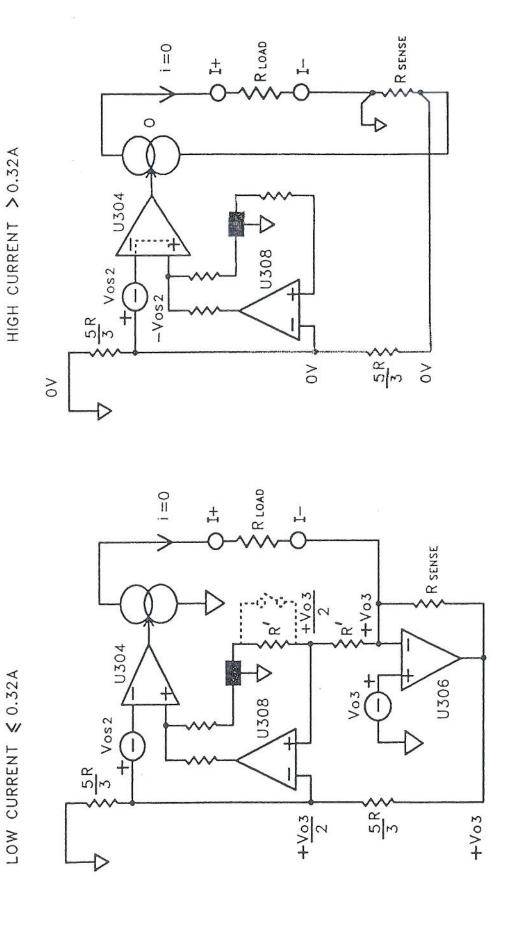

The input network (R301) provides attenuation of the input signal ( $x^{1/3}$ ), analogue switch (U301) impedance matching and a convenient point for the input clamp FET (Q301). With analogue switches, from the same chip, both in the input and the feedback networks, switch ON resistance TC is bucked out.

C302/3 provides the dominant pole in the loop. In open loop mode (J803 pin 2 linked to 3) feedback sense is disabled and local feedback is provided around the error amp by R327 via U302.

DC stabilization is provided by a chopper amp (U308) configured as the low frequency part of a compound amp (crossover approx 1 Hz). At high currents (>0.32A) the chopper amp compares the virtual earth (U304 pin 2) of the loop with reference ground. At low currents (<0.32A) it compares the virtual earth to half the offset voltage of the active ground butter (U306). An analogue switch (U302 pins 9-11) selects the appropriate reference voltage for the DC amp. The virtual earth is sensitve to leakage current so low bias current op amps have been used and pcb guarding employed.

### Small Signal V-I (401096Sht3):

The converter (U305) is formed from an inverting amp, with switched gain (U302) and a class AB output stage. The output voltage is developed across the load resistor (R306), consequently the differential output current, via the collectors of transistors (Q302, 303), is proportional to the input voltage. Diode clamps are provided in the feedback (D308-11) to limit the output current.

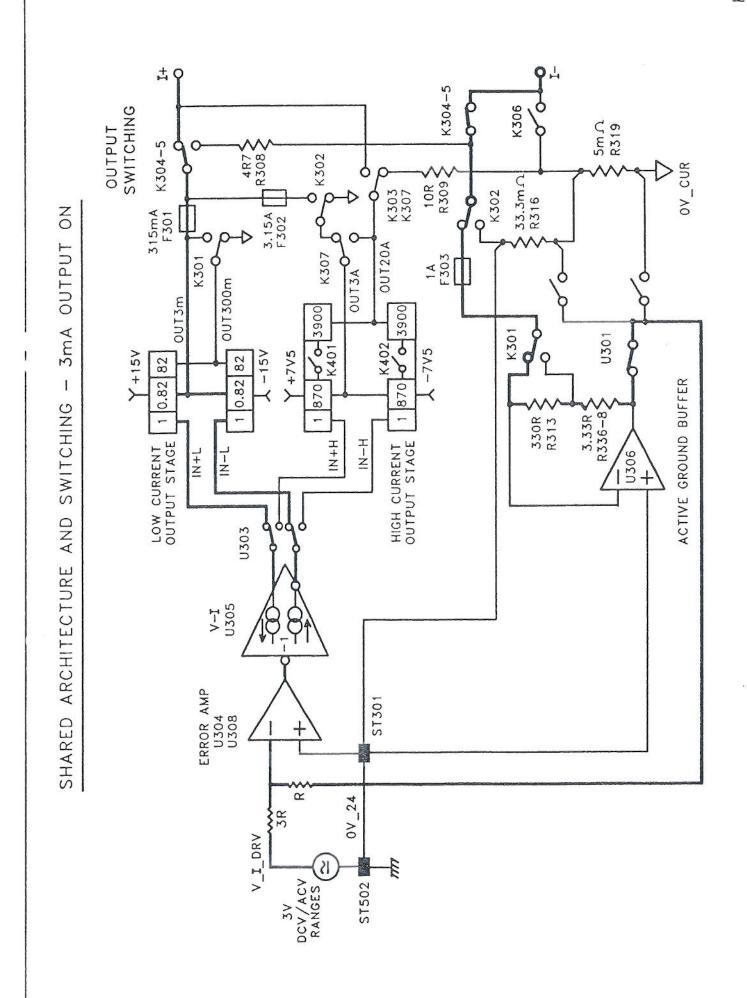

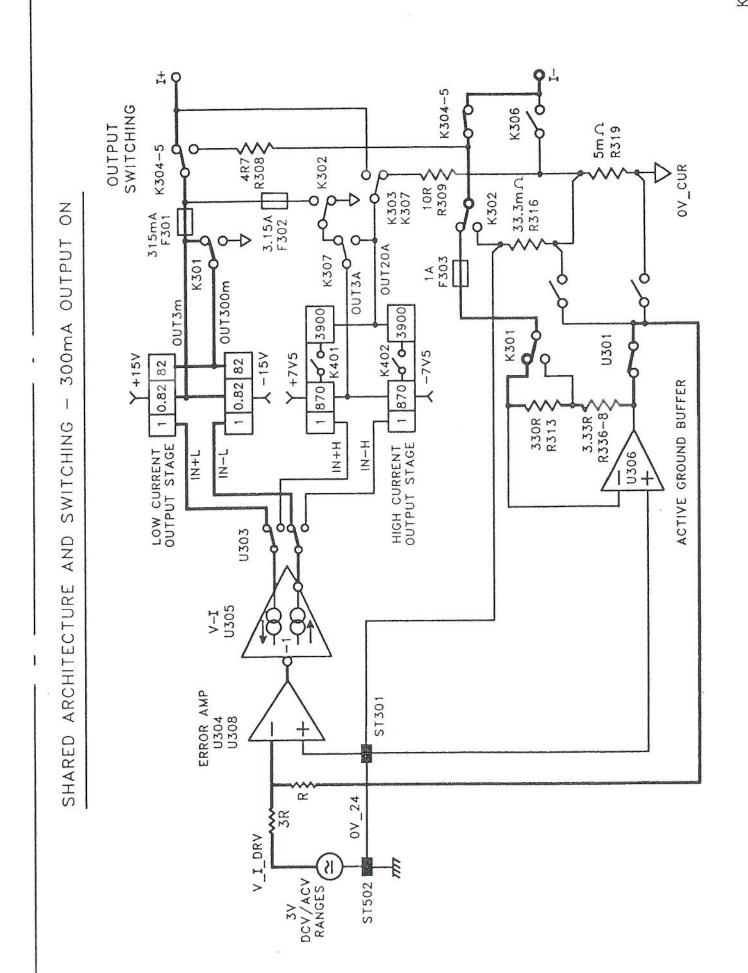

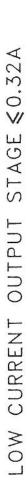

### • Low Current Output Stage (401096Sht4):

The output stage consists of a complementary pair of dual output current mirrors (gains of 0.82 and 82) and a bias current source (Q405). The 3mA range is fed from the low gain output with the high gain output grounded. The 300mA range is fed from both outputs is parallel.

The bias current source maintains a minimum current flow in both both current mirrors when either of the control currents falls to zero. The outputs of the current mirrors are cascoded to increase output impedance. A series RC network (R408 + C404) provides a local HF output current path.

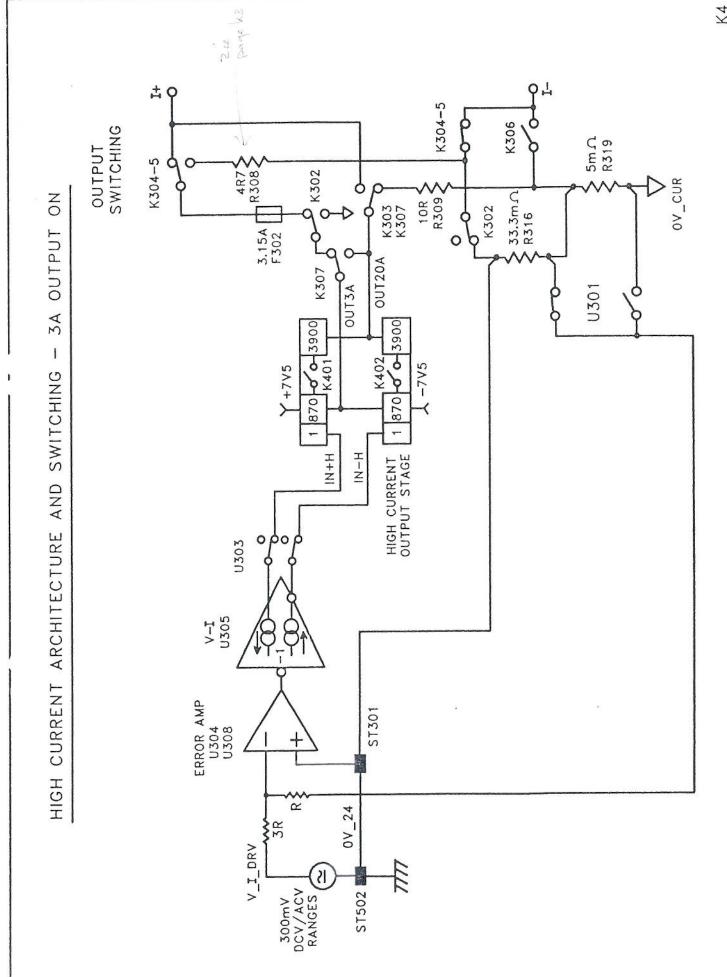

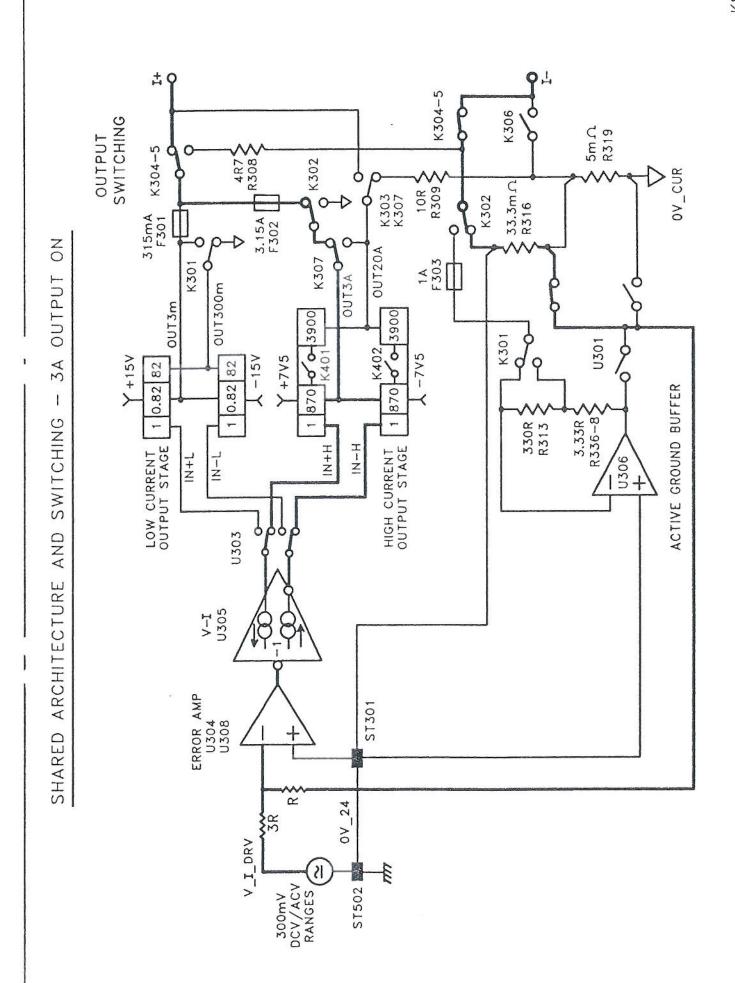

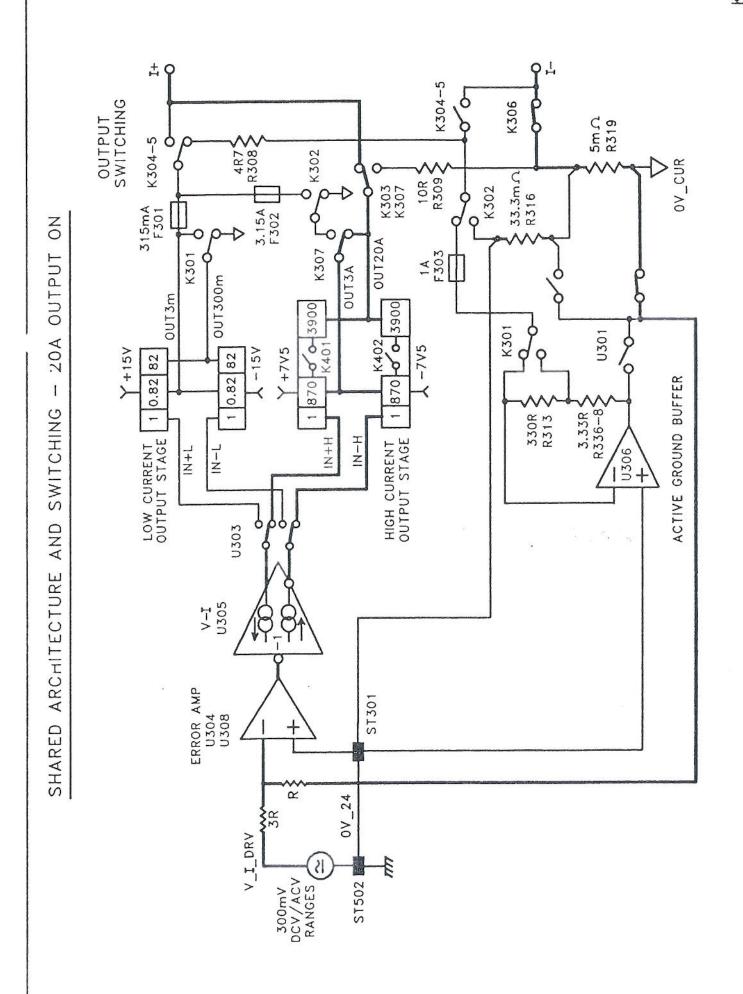

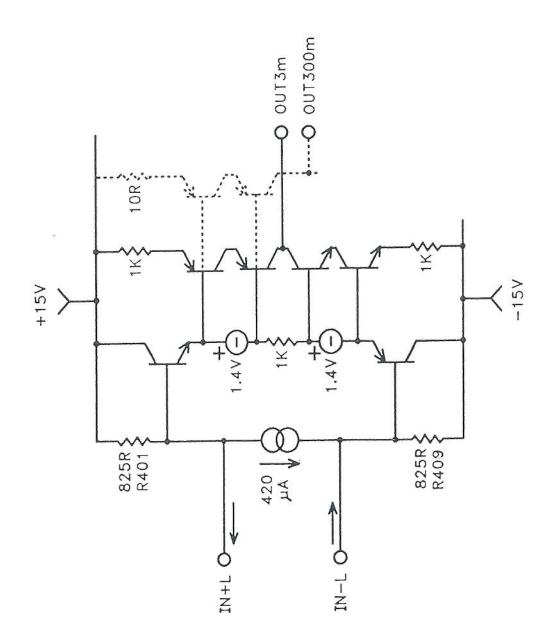

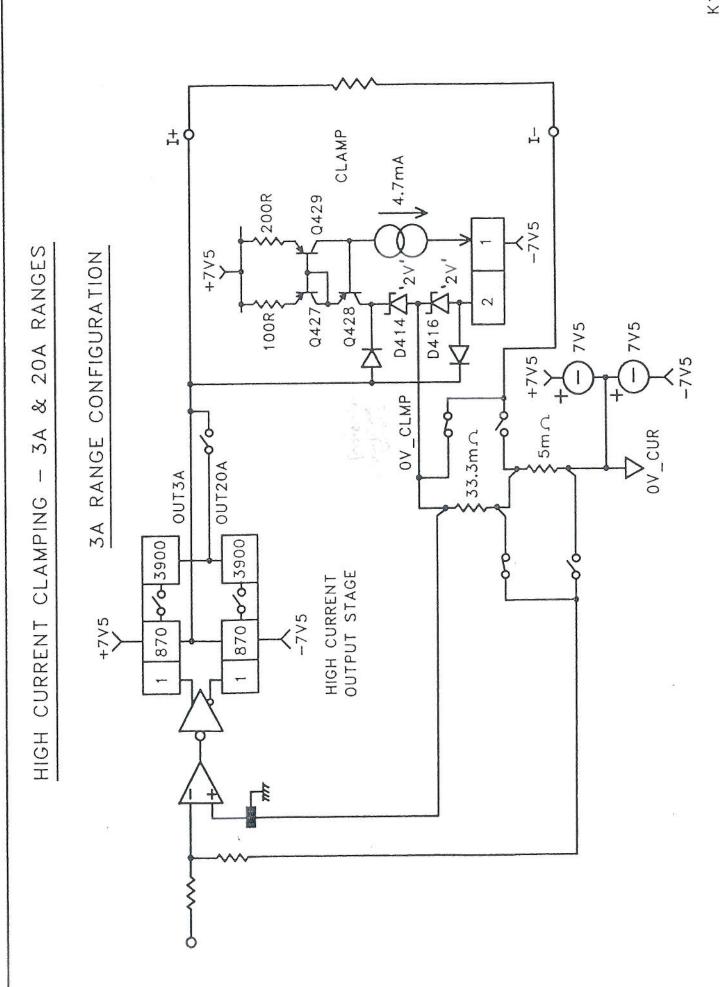

### • High Current Output Stage (401096Sht4) and ±7V5 PSU (401096Sht5):

The high current output stage also consists of a complementary dual output current mirror configuration (gains of 867and 4767) with a bias current source (Q414). The 3A range topology uses one output transistor per mirror whereas the 20A range uses four output transistors per mirror, with the four emitter voltages averaged via R414, 421, 423 and R425. Two relays (K401, K402) isolate the six unused output transistors and their associated feedback signals when in the 3A range configuration.

The ±7V5 lines are conventional unregulated supplies consisting of a transformer secondary, a bridge rectifier and a pair of reservoir caps.

A bipolar, load bypassing, clamp is formed with two zeners (D414, 416) and two diodes (D413, 415). The two zeners are biased up with equal currents which are derived from a current source (Q433) and two current mirrors (Q427-432). In the 3A range configuration the clamp simply provides a parallel path to the load. In the 20A range the clamp current is injected via the top end of the 33mR shunt (R316) not via I-. This forces an output current reduction when the clamp cuts in.

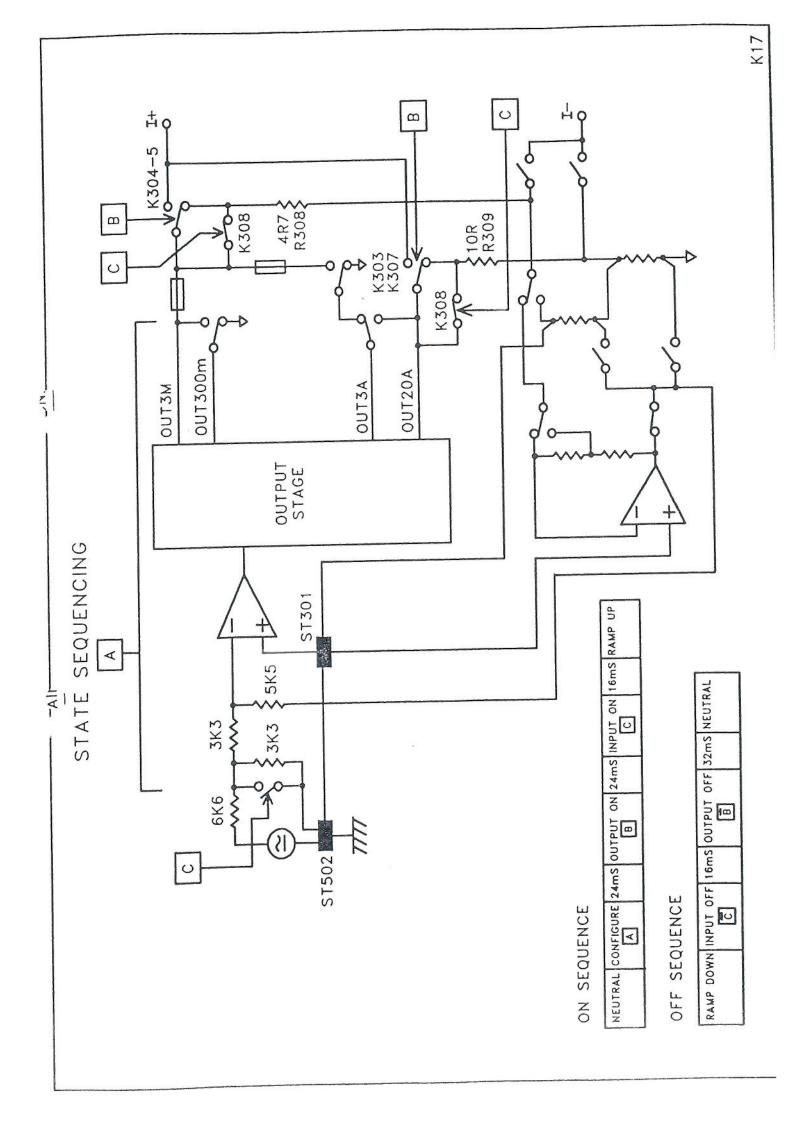

### Output Switching (401096Sht3):

Relays route the appropriate output to either internal loads (4R7/R308 - neutral and self test of 3mA/300mA/3A ranges, 10R/R309 - neutral and self test of 20A) the I+ terminal or the D type guarded current output. Relays route the return current from I- to the appropriate sense resistor. Fuses F301/F302 protect the 3mA, 300mA and 3A outputs. Fuse F303 with diode clamp D305/6 protects the active ground buffer.

Relay K308 maintains connection to the internal loads during the ON sequence whilst the external load is being switched in.

Analogue switch array U301 selects the appropriate feedback signal.

### • Active Ground Buffer (401096Sht3):

The active ground buffer is configured as a ground referenced virtual earth amp. It is formed from an op amp and a class AB, unity gain, output buffer. Relay K301 selects the appropriate feedback resistor (R336-8: 300mA, R313 + 336-8: 3mA).

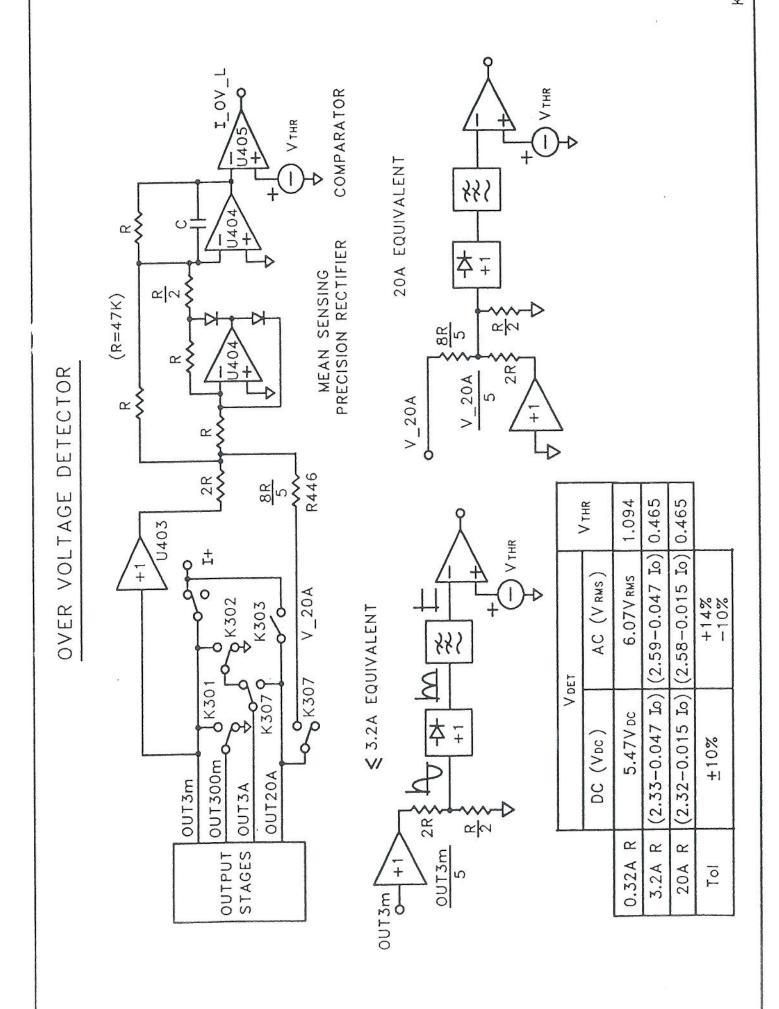

### Over Voltage Detector (401096Sht4):

The over voltage detector consists of a buffer (U403), a precision, unity gain, full wave rectifier/low pass filter (U404) and a comparitor with a switchable threshold (Q434).

The 3mA, 300mA and 3A ranges feed the detector via 'Out 3m' and the 20A range is sensed via 'V-20A'.

The response to the detector is handled via the microprocessor under normal circumstances.

### **FAULT FINDING - CURRENT FUNCTION**

### • $\pm 7$ V5 Supplies:

The  $\pm$  7V5 supplies are high energy and only current limited by the primary fuse. Always be very careful when fault finding with these supplies connected, especially:

- 3A and 20A range faults

- primary side faults

Always check for excessively hot components. The 9000 can be powered up with the  $\pm$  7V5 supplies disconnected (E501, E502). Only the 3A and 20A ranges are affected.

### Bench Supplies:

Fault finding on the 3A and 20A ranges is simpler with external bench supplies in place of the  $\pm$  7V5. Replace internal supplies with:

3AR:

8 - 0 - 8V @ 4A, isolated supply

20AR:

8 - 0 - 8V @ 8A, isolated supply

+8V:

connected to E504

0V:

connected to E506

-8V:

connected to E507

Power on sequence: power up 9000 (with self test disabled - middle horizontal soft key etc) wait 10 s then power up bench supply.

Power off sequence: power off bench supply wait 10 s then power off 9000.

### Self Test:

Factory limit full self test is always a good first pass fault check. This checks for most static functional faults like bias conditions, gains, broken loops, clamps and most of the over voltage detector thresholds. It is important to note that the 20A range over voltage detector is not checked with the self test. So if there is any doubt test this manually.

Self test pathways can be used to access machine states that are otherwise unavailable. The most useful state available is open loop with zero input signal. This state, for each hardware range allows symmetrical bias checking:

300mAR - OL - Ø PO3.001 3mAR - OL - Ø PO3.011 3AR - OL - Ø PO3.014

### Grounding Rules:

For earthy instruments (eg scopes) connect earth clip to either 'chassis metalwork' or TP521 (Star 2). Never connect earth clip to TP302. For floating instruments (eg Dmm) connect 'lo' to TP302 (ground 24) as a general reference.

Due to currents between star points there can be up to 2mVrms between TP302 and TP521.

### Open Loop Configuration:

The open loop mode (J803 to the right) allows functional blocks to be checked without the feedback loop confusing the issue.

Any range can be selected in open loop mode but the current produced at the output is greater than current indicated on the display, so always select the lowest output on the hardware range of interest (eg 0.33A on 3A range) and then use a handheld Dmm as the output load to check the output current before ramping output up to the required level.

Approximate range multipliers in open loop mode:

|            |            | Multiplier | Maximum Displayed Current |

|------------|------------|------------|---------------------------|

| 300µA/3mA  | :          | x 4.2      | 75μA/0.75mA               |

| 30µA/300mA | <b>\</b> : | x 4.2      | 7.5mA/75mA                |

| 3A         | :          | x 1.84     | 1.7A                      |

| 20A        | :          | x 1.52     | 6.5A                      |

### AC Response:

To check the AC loop response of the current converter use the high frequency load regulation tests to check the loop bandwidth is high enough and the maximum load inductance tests to check that the loop bandwidth is not too great. (Tests can be found in the Power board and instrument test procedures.)

### High Frequency High Current Problems:

Always keep output leads short and tightly coupled (eg  $2.5~\text{mm}^2$  conductors twisted together). This will keep the resistance and inductance down. To illustrate the problem at 20A/10KHz the compliance voltage limit (0.9Vrms) is developed across a load inductance of only  $0.7\mu H$ .

Do not be fooled by the voltage waveform on the output as this will appear to be much more distorted than the actual current flowing - The amplification of the

high frequency components of the current is due to the inductive nature of the load. Check the current waveform either with a current probe, or by monitoring TP310 with your scope. The other consequence of this high frequency amplification is that if there is an oscillation, even at low level, the resultant output oscillation voltage will be large. This helps with low level oscillation detection.

# Low Current Problems:

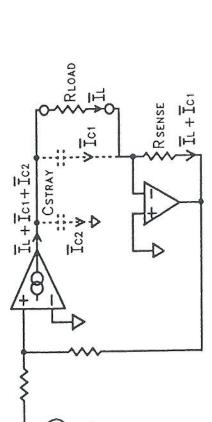

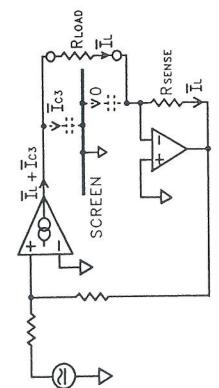

At high frequency stay capacitance can cause large measurement errors. Guarding will reduce the problem (see diagram K19).

At low frequency, problems due to beat noise caused either by pick-up of line harmonic interference or by common mode current, from a line powered measuring instrument, finding its way back to earth via the I- of the 9000. These beats will be worst around 51, 101, 151 Hz etc. The solution to pick-up is screening. To prevent common mode current noise beating use a good quality, well guarded Dmm, eg 1271/81. Also remember battery powered instruments do not generate common mode current.

# **CUSTOMER QUERY ISSUES - CURRENT FUNCTION**

# Inductive Load Handling:

Inductive load handling is limited, especially at high current. It is adequate for reasonable leads and loads, but will not handle inductive loads like multi-turn coils used to calibrate clamp-on ammeters.

# Over Voltage Detector Limits:

Due to the soft nature of the clamps and the tolerance of the detector the trip point is beyond the specified region of operation. Consequently if the output voltage is above the specified region (see Vol II spec section) and below the trip level the output current magnitude will be unreliable.

# Normal and Guarded Output:

Normal output is via I+/I- terminals and guarded output via D type pin 1/I-terminal. Via lead set, yellow and black leads - normal or white and black leads - guarded.

The guarded output is limited to 1A. This output provides a more accurate HF low current output at the lead tips.

# Primary Specifications:

The ACI accuracy specified is for Rms measurement, therefore on mean sensing instruments the mean sense error must be added to the overall accuracy. Mean sense instruments are generally of much lower accuracy so the TURs are not affected significantly.

# Low Current Output:

For pick-up and common mode current issues see "Fault Finding".

# Earthed Instruments:

As the 9000 is earthed it will only operate properly with an isolated load.

# Scope Option

# Guided Tour

# Contents

**Block Diagram**

Summary Descriptions

**Detailed Functional Paths**

Factory Test Procedure

Procedure

Self Test

Circuit Diagrams

Layout

# Scope Calibration Module.

- Block diagram description of functional configurations. 1.

- Sine 10Hz to 250MHz. 1.1

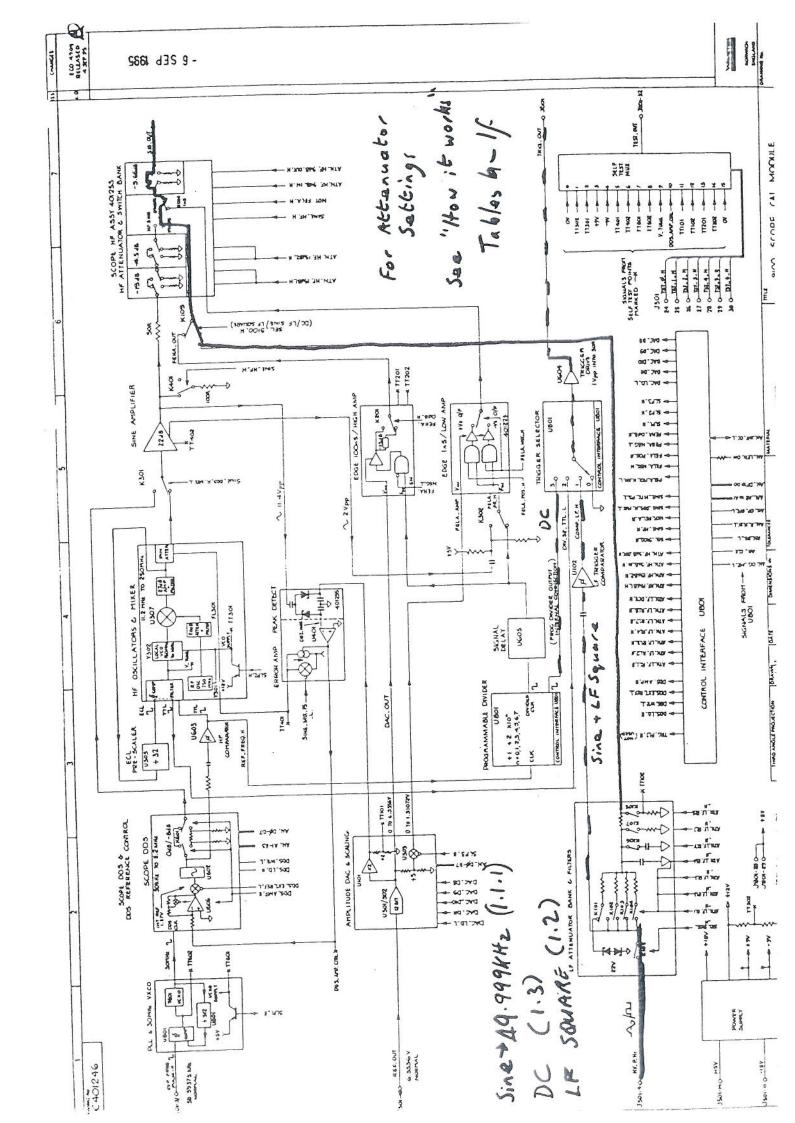

# 1.1.1 Sine 10Hz to <50kHz. (49.999 KHz)

The power and analogue assemblies are used to generate sine waves of a particular amplitude and required output frequency. The front terminal output relays remain open and the scope module connects to the signal HV\_P\_HI on the 50 way analogue ribbon connector.

This signal is routed to SIG\_OUT via the LF attenuator and last stage of the HF attenuator. The final stage of the HF attenuator also acts as the output on/off relay.

The trigger output, TRIG\_OUT, is driven at the same frequency as SIG\_OUT by the AC coupled trigger comparator, U102, sensing HV\_P\_HI. Its output is routed to TRIG\_OUT via the Actel device U801.

The phase of the trigger and signal may change with 9100 setting (e.g. range & frequency).

The 30MHz VCXO and HF oscillators sleep in this mode to reduce noise.

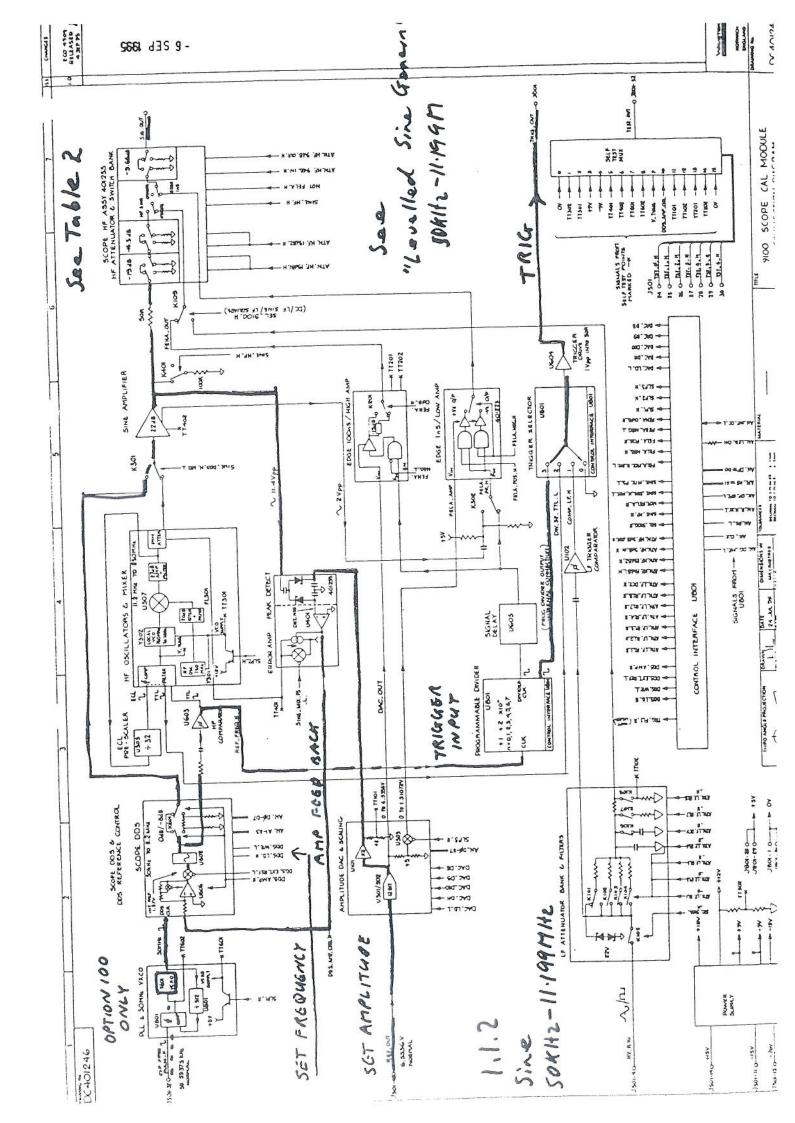

# 1.1.2 Sine 50kHz to <11.2MHz.

The scope DDS, U602, is used to generate a sine wave signal of the required frequency and variable amplitude. This is amplified then routed to SIG\_OUT via the HF attenuator.

The amplitude level is controlled by a loop which drives the DDS reference. The DDS reference can be over driven by an external signal (OV to 2V). The peak detector on the scope HF assembly and error amplifier compare the set point from the amplitude DAC and scaling with the buffer output to complete the amplitude loop.

At lower amplitudes the DDS has an 8dB input amplifier and -8dB output attenuator to keep its reference at a sensible level. Lower amplitude is decoded by the Actel device, U801, when the latched bits driving the amplitude DAC\_D11 to DAC\_D8 have the binary code 0 1 0 1 or less.

The DDS is driven at 30MHz by either a 30MHz VCXO or 30MHz +-25ppm fixed oscillator. The VCXO is fitted when option 100 is fitted to the analogue assembly to maintain the frequency specification. A phase lock loop is used to lock the analog assy signal EXP\_FREQ\_PULSE\_H at 58.59375kHz to the 30MHz required for the DDS. The 32 bit scope DDS has 6.99mHz resolution which is 0.139ppm of 50kHz, so small frequency adjustments to the analog assembly DDS are made to get the accuracy well within the 0.25ppm specification of option 100. If the fixed crystal is fitted the frequency corrections to EXP\_FREQ\_PULSE\_H have no effect.

When EXP\_FREQ\_PULSE\_H is used the main DAC on the analogue assembly is set for minimum frequency/pulse output amplitude as the output stage will still be active.

The trigger signal is derived from the AC coupled comparator, U603, sensing the scope DDS output. The follower Q602 is used to stop noise feeding back to the filter. It is routed to TRIG\_OUT via the progammable divider (set to divide by one) and trigger selector in the Actel device U801.

The HF oscillators sleep in this mode.

1

# 1.1.3 Sine 11.2MHz to <250MHz.

A high frequency signal is generated by a mixer arrangement controlled by a phase lock loop and an amplitude loop. The signal is amplified and routed to SIG\_OUT via the HF attenuator.

The output frequency is 32 times the scope DDS frequency (0.350MHz to 7.8125MHz) and adjusted by changing the scope DDS setting (and the analog assembly DDS if the VCXO is fitted). The scope DOS run at higher amplitude from its internal voltage reference as it only provides a frequency reference. The external reference is it is isolated by U807-1/2/3.

The level is set by a control loop which drives a pin attenuator on the mixer output. The peak detector and error amplifier compares the set point from the amplitude DAC with the buffer output to complete the amplitude loop.

The trigger signal is derived from the signal frequency divided by 32. It comes from the prescaler U303 and level shifter Q407/Q408. It is routed to TRIG\_OUT via the Actel device U801. Delays in the circuitry may cause frequency dependant phase shifts between SIG\_OUT and TRIG\_OUT.

# Square 1kHz.

The square uses the same path as the sine for 10Hz to 50kHz. The signal is generated at 1kHz only by the power and analogue assemblies.

The analog assembly DDS is loaded with a new pattern so that the base of the square is related to 0V and adjustment will be made to its peak value using the analog assembly main DAC.

The trigger is generated at 1kHz and being AC coupled should line up with SIG\_OUT.

The 30MHz VCXO and HF oscillators sleep in this mode.

### DC. 1.3

DC uses the same path as the sine 10Hz to 50kHz. The power and analog assemblies generate the DC signal. The LF attenuator includes a filter, C105, which is selected for higher DC voltages using the HF transformer.

The 30MHz VCXO and HF oscillators sleep in this mode.

A trigger signal at approximately 64Hz is generated within the Actel device, U801, using the clock AN\_CLK.

### 1.4 Edge.

# 1.4.1 Edge 1ns/low amplitude 10ms to 89.29ns.

The edge Ins/low amplitude output circuitry drives SIG\_OUT via the HF attenuator which also provides the output on/off relay.

The repetition period of the output is determined by the scope DDS, U602, which drives through the programmable divider on the Actel device, U801. This combination gives variability in decades without introducing excessive DDS uncertainty at lower frequencies. The scope DDS clock is generated by either the 30MHz VCXO locked to EXP\_FRQ\_PLS\_H.or the fixed crystal The DDS is set to a higher output amplitude using its internal reference.

The output amplitude is set by the amplitude DAC and scaling which drives the edge 1ns/low amplitude output stage directly.

Triggers are generated from the programmable divider output within the Actel device and routed to TRIG\_OUT. Signal delay is added by a U605 to ensure that the trigger occurs before the edge.

The HF oscillators should sleep in this mode.

# 1.4.2 Edge 1ns/low amplitude 89.29ns to 10ns.

This mode uses the sine circuitry (11.2MHz to 100mhz) to drive the edge output circuits.

The repetition period of the output is determined by the scope DDS but the frequency is multiplied by 32 using the HF oscillators and mixer. Minimum attenuation on the mixer output is set by Jamming the peak detector and error amplifier to get FS output using U503/14/15/16..

Triggers are generated from the ECL pre-scaler so occur every 32 edges of the output signal.

# 1.4.3 Edge 100ns/high amplitude 10ms to 10us.

This mode is similar to edge 1ns/low amplitude 10ms to 89.29ns with amplitude and repetition rate routed to the edge 100ns/high amplitude output circuitry, instead of the 1ns/low amplitude.

The HF oscillators sleep in this mode.

### Markers 5.5s to 4ns. 1.5

1

# 1.5.1 Markers 5.5s to 89.29ns.

This mode uses the same configuration as edge 1ns/low amplitude 10ms to 89.29ns. The lower range is extended to 5.5 seconds by more programmable divider stages.

# 1.5.2 Markers 89.29ns to 8.8888ns.

This mode uses the same configuration as edge 1ns/low amplitude 89.29ns to 10ns.

# 1.5.3 Markers 8.8888ns to 04.000ns.

This mode uses the same configuration as sine 11.2MHz to 250MHz. It is actually a sine so the trigger point may vary compared to the other markers.

# Circuit descriptions -sheet by sheet. 2.

### Sheet 1 2.1

Relays shown are driven from circuits on sheet 8 |The comparator U102 senses HV\_P\_HI to derive triggers when the analog and power assemblies are sourcing the scope module output.

### Sheet 2 2.2

Signal DLY\_LINE\_OUT\_H controls the switching of the edge 100ns/high amplitude. FEHA\_NEG\_L goes low to enable circuitry.

### Sheet 3 2.3

Signal SLP2\_H is used to enable the oscillators. The pre-scaler U303 is used to drive PLL on sheet 4. Relay K302 allows the edge 1 ns/low amplitude to be driven from the sine output above 11.2MHz or DLY\_LINE\_OUT\_H below 11.2mhz.

### Sheet 4 2.4

Signal SINE\_MIX\_FS\_L is used to get minimum attenuation from pin attenuator, hence maximum amplitude to drive edge circuitry

### Sheet 5 2.5

DAC U501 is used to control amplitude of waveforms generated on the scope assembly. The most significant four bits are latched by Actel device U801 and remain static. They are clocked into DAC when the processor writer the least significant eight bits by strobing DAC\_LD\_L. The DAC is driven from the analog assembly reference at 6.5536V which gives a ouput between 0V and 8.5536V.

The DAC output is divided by four to drive the edge circuitry. Signal SLP3\_H is high when the edge 1ns/low amplitude when not used.

### Sheet 6 2.6

The DDS, U602 and filter on U60-2 are used to generate sine waves between 50kHz and 11.199MHz. The DDS has an internal reference of 1.27V on U605-8 which is enabled when switch U807-1/2/3 is open.. When U807-1/2/3 is closed the internal reference is overdriven by the amplitude control signal from the peak detector and error amplifier, DOS\_AMP\_CTRL. At lower amplitudes the amplifier U606 gives a gain of x2.5 to the reference level and there is a corresponding attenuation from K301-4/7, to help reduce noise effects. The diode clamps, D607 and D608, stop U602-6 going outside the range 0V to +2V. The DDS output U602-2 should always be in the range OV to 1V.

Follower Q602 and comparator U603 generate a logic signal at the same frequency as the sine wave on REF\_FREQ\_H. This is used to drive the x32 PLL or programmable divider on Actel device U801-84.

The trigger output stage is a logic gate U604 which gives 1Vpk into 50R external load. The trigger source is selected by Actel device U801 from:-

- programmable divider divide by 1, 2, 20, 200 etc. to 20000000,

- COMPL\_LF\_H for signals power and anlog assemblies or 2

- DIV\_32\_TTL\_L for outputs frequecies above 11.2MHz. 3

The programmable divider output U801-63 is delayed by U605 to ensure that the edge outputs occur later than the trigger output.

The DDS clock comes from 30MHz VCXO Y601 (which may be a fixed cryts) when option 100 is not fitted). The VCXO is phase locked to EXP\_FREQ\_PULSE\_H at 58.59375kHz from the analog assembly. The VCXO divide by 512 and phase comparator are on Actel device U801. The fast and slow control outputs are summed and filtered at C812, which feeds back to the VCXO via amplifier U601.

The supply to the VCXO is switched by Q601 to reduce noise when the DDS is not required. D605 and D606 ensure U601 does not drive the VCXO when its power supply is switched off. SLP1\_H also reduced the DDS DAC consumption by driving U602\_37.

The DDS registers are written by the processor via AN\_D7 to AN\_D0 which are strobed by DOS\_WR\_L. Bytes are written in groups to fill a four byte assembly register. The assembly register is transferred to the required destination by AN\_A3 to AN\_A1 which are strobed by DOS\_LD\_L (this should be active high). The DOS clock must be present for loading to work properly.

# Sheet 7

1

1 .

The self test selection signals TST\_6\_H to TST\_0\_H from the analog and power assemblies, control analog multiplexers U701 and U702.

# Sheet 8

Actel device U801 contains the double latching for the 32 relay and control bits. The latches are written in groups of four bytes so the last write updates the control outputs. The control bits are written from data on AN\_D7 to AN\_D0, decoded address AN\_A8 to AN\_A1 and the strobe AN\_DS\_L. The signal AN\_R\_H\_W\_L is high to read and low to write the registers.

The signal AN\_I\_OC\_L is an open collector interrupt line which signals the processor and other Adel devices that the detector input U801-42 has latched. Adel devices on other assemblies can drive this line. If the interrupt is ignored all Actel devices will force a safe instrument control bit state after 0.25 seconds from the interrupt line first going low. The signal AN\_OP\_OFF\_L is pulsed low when the off key is pressed to check that the firmware services it. It will force a safe state 0.5 seconds after it is first seen if the firmware does not respond.

The signal; AN\_LED\_ON\_L tums on the front panel red LED. It is driven low by Actel devices on other assemblies including the scope module when an output is turned on. When a high voltage control pattern is selected the power assembly Actel device will drive this signal to about 3V once per second to flash the LED off.

# Control bit names and functions.

These names are for register bits within the Actel device U801 with the pin numbers they drive shown in brackets. They may be useful when fault finding.

# LF Attenuator Bank and Filter

The following bits are decoded for sine 10Hz to 50kHz, DCV and square 1kHz. They control the LF Attenuator which is used only when the power and analogue assemblies are to drive the scope option output.

| Scope | option e-4   |           | [83] |

|-------|--------------|-----------|------|

| S1-0  | ATN_LF_RL1_H | default=L |      |

|       | ATN_LF_RL2_H | default=L | [31] |

| S1-1  | ATN_LF_RL3_H | default=L | [1]  |

| S1-2  | ATN G TILS   | default=L | [80] |

| S1-3  | ATN_LF_RL4_H | default=L | [6]  |

| 51-4  | ATN_LF_RL7_H |           | isi  |

| \$1-5 | ATN_LF_RL8_H | default=L |      |

|       | ATN_LF_DCV_H | default=L | [3]  |

| S1-6  | 0100 H       | default=L | [2]  |

| S1-7  | SEL_9100_H   |           |      |

# HF Attenuator Bank and Output Relay 3.2

ATN\_HF\_19dB\_1\_H default=L inserts 19dB attenuator 1 for sine 50kHz to 250MHz. S2-0 H attenuator 1 bypassed. L

ATN\_HF\_19dB\_2\_H default=L inserts 19dB attenuator 2 for sine 50kHz to 250MHz. S2-1 H attenuator 2 bypassed. L

The following bits are decoded to select 9.66dB attenuator and perform output on:-

| S2-2 | ATN_HF_9dB_IN_H (76)<br>ATN_HF_9dB_OUT_H (77) | output off<br>(default)<br>L | output on<br>9 66dB atten<br>L<br>H | output on<br>no atten<br>H<br>L |

|------|-----------------------------------------------|------------------------------|-------------------------------------|---------------------------------|

| S2-3 |                                               | L                            | n                                   |                                 |

## Trigger Control 3.3

| 3.3          | Trigger Control                     | disabled<br>(default) | sine 10kHz<br>to 50kHz - IP1 | output<br>freq / 32 - 1P2 | prog.<br>divider |

|--------------|-------------------------------------|-----------------------|------------------------------|---------------------------|------------------|

|              | FO H Inc Nini                       | 0                     | 1                            | 0                         | 1                |

| S2-4<br>S2-5 | TRG_F0_H [no pin] TRG_F1_H [no pin] |                       | 0                            | 1                         | 1                |

| S2-6<br>H | TRG_FLT_H (not used) trigger filter active trigger filter inactive. | default=L | [13] |

|-----------|---------------------------------------------------------------------|-----------|------|

| L         | night.                                                              |           |      |

```

[no pin]

default=L

TRG_INV_H

S2-7

trigger output is inverted

H

trigger output not inverted.

L

Edge 1ns/Low Amplitude and 100ns/High Amplitude

3.4

FELA_MIX_H_DIV_L default=L

drives edge low amplitude from the DDS & mixer (50kHz to 11.2mhz).

S3-0

drives edge low amplitude from the programmable divider delay line.

H

L

FELA_POS_H (do not select with NEG) default=L

configures edge low amplitude for positive output pulse.

S3-1

disables edge low amplitude positive output.

H

FELA_NEG_H (do not select with POS) default=L

configures edge low amplitude for negative output pulse.

S3-2

disables edge low amplitude negative output.

H

L

[79]

FEHA_NEG_L default=H

disables edge high amplitude negative output.

S3-3

configures edge high amplitude for negative output pulse.

H

L

FEHA_ODB_H defauit=L

[7]

de-selects attenuation of edge low amplitude.

53-4

selects -15dB attenuator for edge high amplitude negative output.

H

L

[8]

SPARE S3_5

S3-5

[21]

SPARE S3_8 default=L

S3-6

drives edge frequency inputs high to stop noisy signal toggling and for for test.

FE_TST_H

S3-7

allows edge inputs to be driven form selected source.

H

L

General Signal Routing.

3.5

connects sine 50kHz to 250MHz from mixer or DDS to output circuitry.

default=L

[53]

SINE_HF_H

S4-0

other functions connected to output circuitry.

H

L

SINE_DDS_H_MIX_L default=L

connects DDS to output circuitry for sine 50kHz to 11.2MHz.

S4-1

connects mixer to output circuitry for sine 11.2MHz to 250MHz.

H

L

[62]

default=L

SINE_MIX_FS_L

normal sine 50kHz to 250MHz amplitude loop operation.

$4-2

drives the sine 50kHz to 250MHz amplitude control loop to maximum output.

H

```

[70] DOS\_EXT\_REF\_L DDS internal reference for use as frequency source without amplitude control. default≖H closes amplitude loop for sine 5kHz to 11.2MHz. H L S4-4 NOT\_FELA\_H default=L [11] other functions connected to output circuitry. H connects edge low amplitude to output circuitry. Sleep Control. 3.6 [10] default=H SLP1\_H 54-5 30MHz VCXO to sleep mode. H 30MHz VCXO enable. L [15] default=H SLP2\_H S4-8 HF oscillators to sleep mode. H HF oscillators enable. L

S4-7 SLP3\_H default=H [81]

H edge low amplitude to sleep mode.

L edge low amplitude enable.

t

.

1

# Scope Actel Registers. 4.

The scope Actel device controls the address decoding for the DDS, DAC and control bits. Readback is only provided on the four control bit registers and the status register.

The S CLR address should be cleared in the same way as the P CLR and A CLR in the power and analogue devices. There is a spare detector and the same off key time-out and hardware go to neutral (should the common signal generation interrupt not be serviced by the processor) system as the other devices.

The programmable divider is a cascaded decade counter. The taps are selected by the programmable divider register.

### Status Register 4.1

This is decoded as follows:-

SR-0 OFF\_TIMEOUT\_H

output off key time-out has occurred or the hardware has gone to neutral as the interrupt was not serviced.

S\_DET\_H SR-1

detector has tripped causing interrupt and starts go to neutral time-out. H

SR-2 OPT\_TST\_L

option not fitted H

option fatted

# Programmable Divider 4.2

Bits 3 to 0 are decoded as follows:-

| Bits 3 to 0 are de | PD-3 | PD-2 | PD-1          | PD-0 |

|--------------------|------|------|---------------|------|

| 27 27 UV           | 0    | 0    | 0             | 0    |

| 1/1 (default)      | 0    | 0    | 0             | 1    |

| IF_CLK (64Hz)      | 1    | 0    | 0             | 0    |

| 1/2                | 1    | 0    | 0             | 1    |

| 1/20               | 1    | 0    | 1             | 0    |

| 1/200<br>1/2000    | 1    | 0    | 1             | 1    |

| 1/20000            | 1    | 1    | 0             | 0    |

| 1/200000           | 1    | 1    | 0             | 1    |

| 1/2000000          | 1    | 1    | 1             | 0    |

| 1/20000000         | 1    | 1    | 1             | 1    |

|                    |      |      | anna function |      |

IF\_CLK is used to provide a trigger output in DCV scope function.

The output of the programmable divider drives the edge circuitry via pin 63 and/or the trigger via pin 14

## Control Bit Registers 4.3

These registers are described above as S!, S2, S3 & S4. They can be written and read and are double latched so writing S4 (possibly using MOVEP.L) will change the control bits to the new state. The read is of the second latch driving the output pin levels.

### Scope DAC 4.4

This DAC is written (possibly using MOVEP.W) as a high byte containing D11 to D8 and a low byte containing D7 to D0. The high byte is tatched and transferred to the DAC when the low byte is written.

### DDS Registers 4.5

1

The DDS assembly register is used to temporarily hold values to be written to the DDS registers.